# DRV8462: 65 V, 5-10 A Stepper Motor Driver for High Efficiency and Noiseless Operation

## 1 Features

- Stepper motor driver

- SPI or H/W interface with STEP/DIR pins

- Up to **1/256** microstepping indexer

- **4.5 V to 65 V** operating supply voltage range

- Supports standard 24 V, 36 V and 48 V rails

- Low  $R_{DS(ON)}$ : **100 mΩ** HS + LS at 24 V, 25°C

- High current capacity per bridge:

- DDW Package: **5A** full-scale, 3.5A RMS

- DDV Package: **10A** full-scale, 7A RMS

- DDW package **pin-to-pin compatible** with -

- **DRV8452DDWR**: 48 V, 5A full-scale

- **DRV8461DDWR**: 65 V, 3A full-scale

- Integrated current sensing and regulation

- **5%** full-scale current accuracy

- Smart tune and mixed decay regulation options

- **Silent step** decay mode for silent operation at standstill and low speed

- **Automatic Microstepping** mode for step frequency interpolation

- **Customizable microstepping** indexer table

- **Auto-torque** for load dependent current control

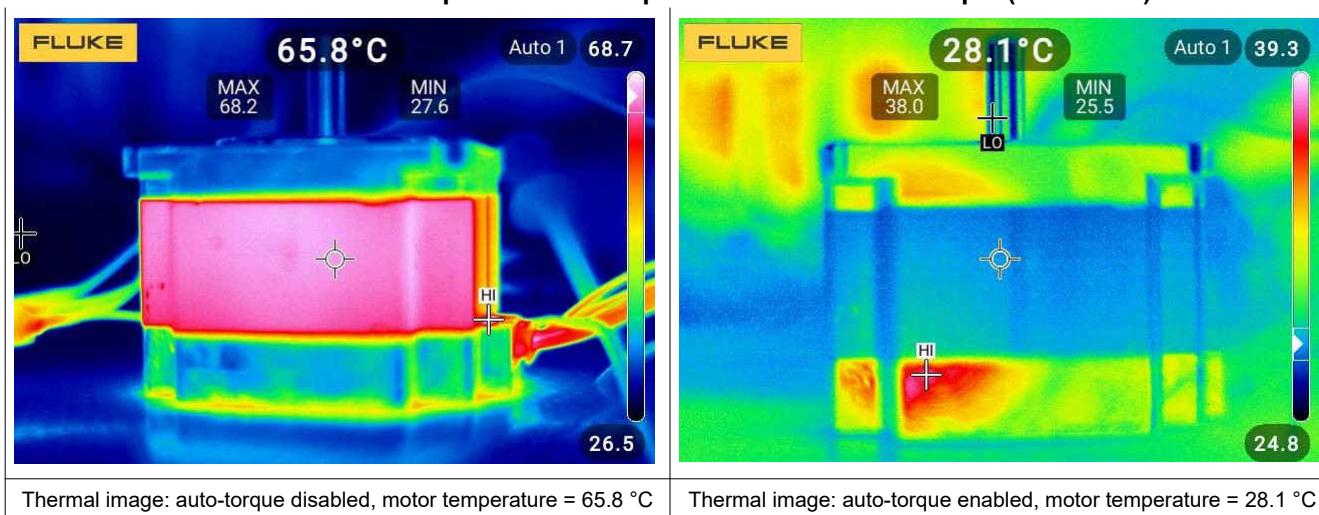

- **Standstill Power Saving** mode

- Supports 1.8-V, 3.3-V, 5.0-V logic inputs

- Low-current sleep mode (3  $\mu$ A)

- Separate logic supply voltage (**VCC**)

- Protection and diagnostic features

- Sensorless **Stall Detection**

- VM undervoltage lockout (UVLO)

- Open-load detection (OL)

- Overcurrent protection (OCP)

- Thermal shutdown (OTSD)

- Fault condition output (nFAULT)

- Indexer zero position output (**nHOME**)

## 2 Applications

- **Textile Machines**, Sewing machines

- **Factory Automation, Stepper Drives and Robotics**

- **Medical Imaging, Diagnostics and Equipment**

- **Stage Lighting**

- **ATMs, Currency Counters**

- **PLC, DCS & PAC**

- **Multifunction Printers**

- **3D Printer**

- **Outdoor IP Camera**

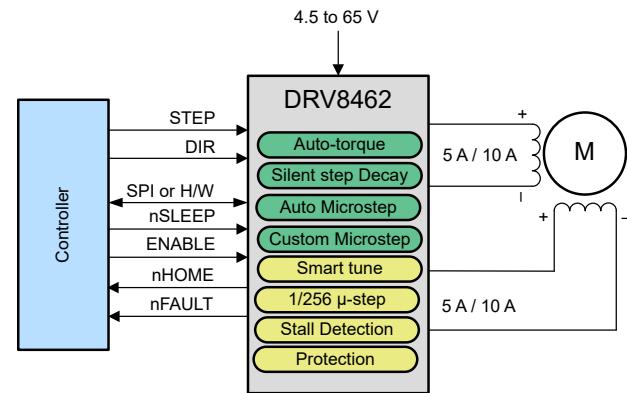

## 3 Description

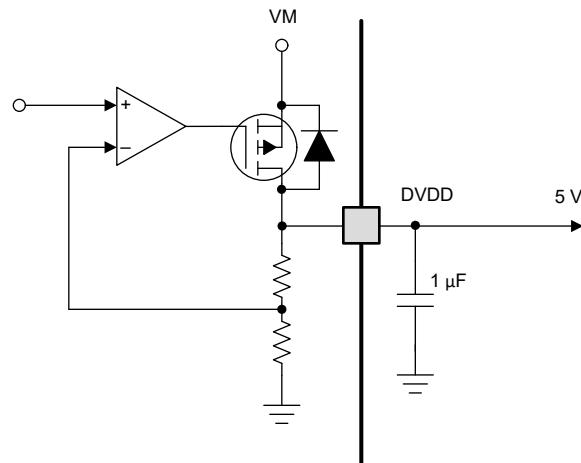

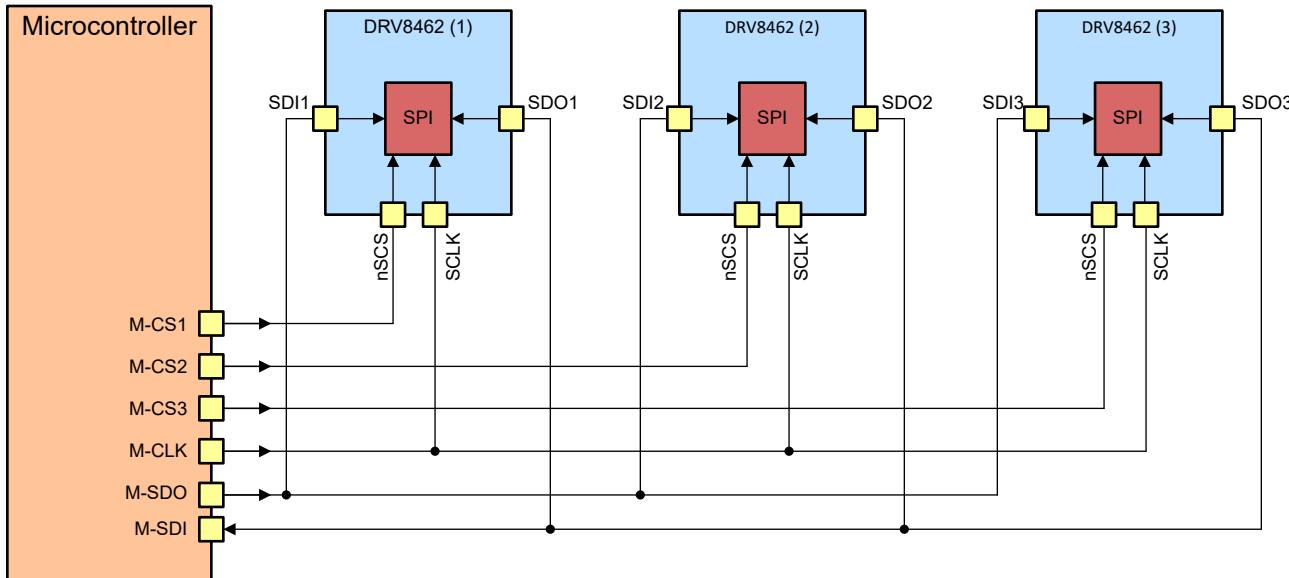

The DRV8462 is a wide-voltage, high-power, high-performance stepper motor driver. The device supports up to 65-V supply voltage, and integrated MOSFETs with 100 mΩ HS + LS on-resistance allow up to 10-A current.

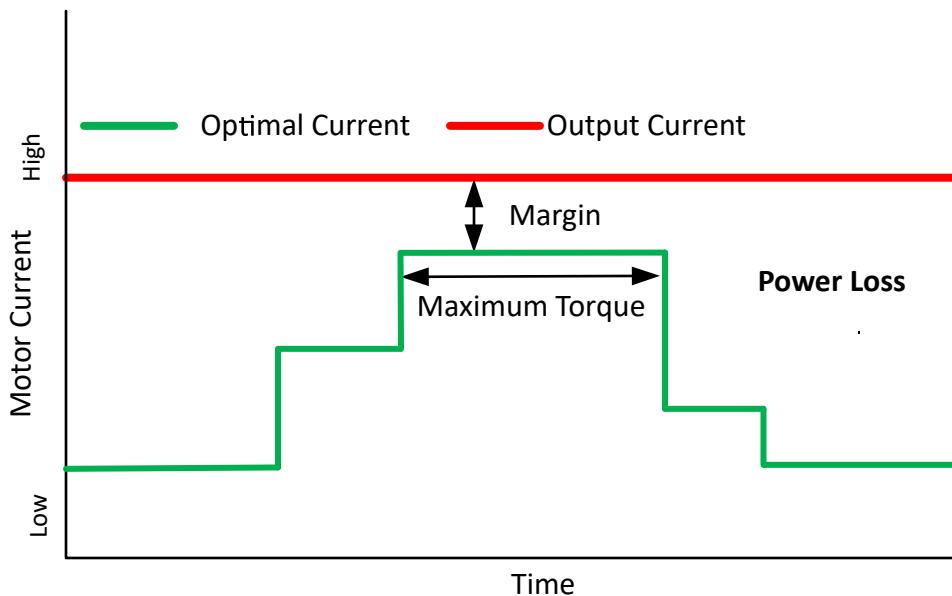

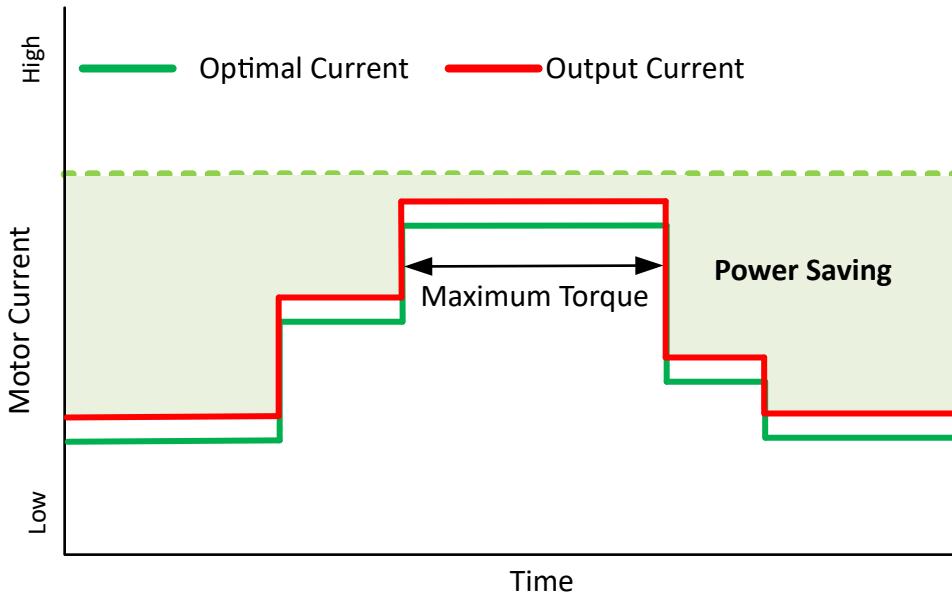

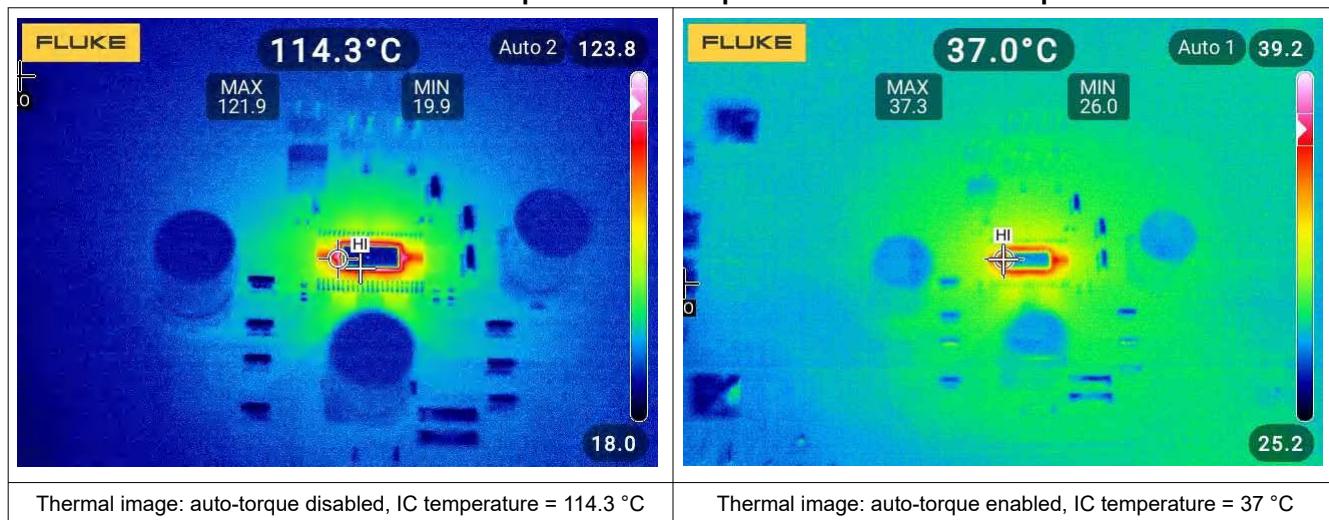

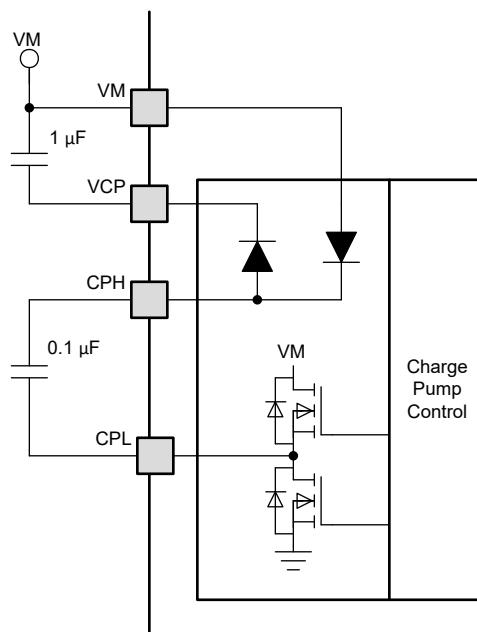

The auto-torque feature boosts efficiency by adjusting the coil current according to load torque. Standstill power saving mode reduces power loss during motor holding condition. Silent step decay mode guarantees noiseless operation at low speeds and standstill. The internal current sense eliminates the need for sense resistors, saving PCB area and system cost. Built-in indexer supports up to 1/256 microstepping, and the automatic microstepping mode interpolates the input STEP signal to reduce overhead on the controller. Sensorless stall detection eliminates end stops from the system. The device supports other protection and diagnostic features for robust and reliable operation.

The DRV8462 requires minimal tuning to configure the advanced features. It supports higher power density compared to external FET drivers, with a smaller PCB area. High energy efficiency with precise, noiseless operation makes the DRV8462 an ideal choice for high-performance stepper systems.

### Device Information

| PART NUMBER | PACKAGE <sup>(1)</sup>          | BODY SIZE (NOM) |

|-------------|---------------------------------|-----------------|

| DRV8462DDWR | HTSSOP (44), bottom exposed pad | 14 mm x 6.1 mm  |

| DRV8462DDVR | HTSSOP (44), top exposed pad    | 14 mm x 6.1 mm  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

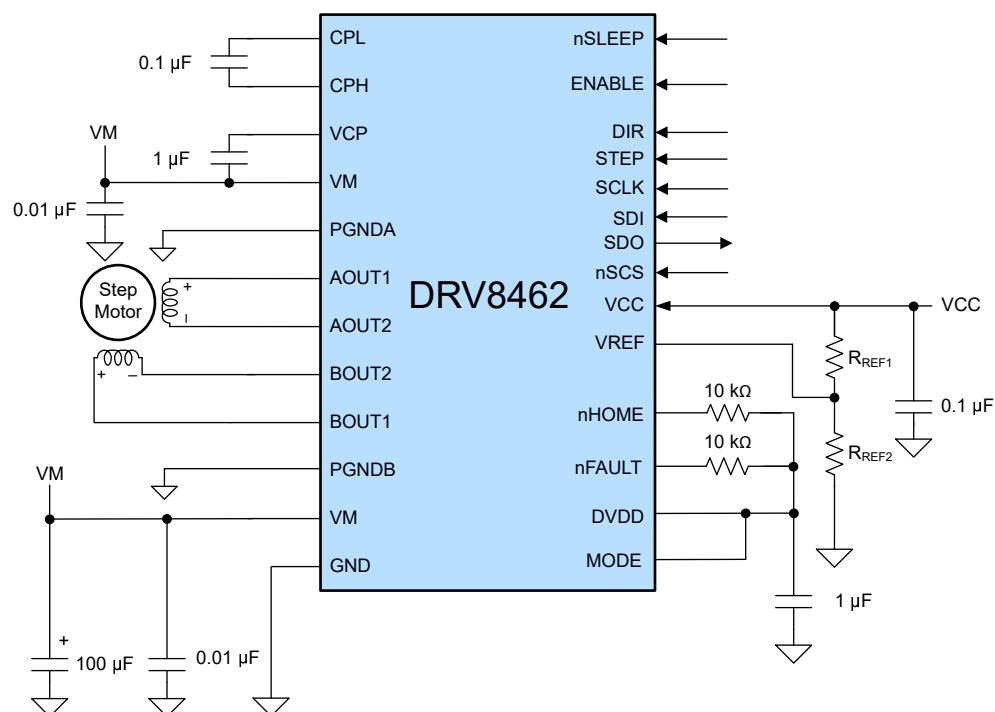

**Simplified Schematic**

An **IMPORTANT NOTICE** at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. **PRODUCTION DATA**.

## Table of Contents

|                                                |            |                                                                            |            |

|------------------------------------------------|------------|----------------------------------------------------------------------------|------------|

| <b>1 Features</b> .....                        | <b>1</b>   | 8.2 Typical Application.....                                               | <b>101</b> |

| <b>2 Applications</b> .....                    | <b>1</b>   | <b>9 Thermal Considerations</b> .....                                      | <b>108</b> |

| <b>3 Description</b> .....                     | <b>1</b>   | 9.1 DDV Package.....                                                       | <b>108</b> |

| <b>4 Revision History</b> .....                | <b>2</b>   | 9.2 DDW Package.....                                                       | <b>109</b> |

| <b>5 Pin Configuration and Functions</b> ..... | <b>3</b>   | 9.3 PCB Material Recommendation.....                                       | <b>109</b> |

| <b>6 Specifications</b> .....                  | <b>6</b>   | <b>10 Power Supply Recommendations</b> .....                               | <b>110</b> |

| 6.1 Absolute Maximum Ratings.....              | 6          | 10.1 Bulk Capacitance.....                                                 | <b>110</b> |

| 6.2 ESD Ratings.....                           | 6          | 10.2 Power Supplies.....                                                   | <b>110</b> |

| 6.3 Recommended Operating Conditions.....      | 6          | <b>11 Layout</b> .....                                                     | <b>111</b> |

| 6.4 Thermal Information.....                   | 7          | 11.1 Layout Guidelines.....                                                | <b>111</b> |

| 6.5 Electrical Characteristics.....            | 8          | 11.2 Layout Example.....                                                   | <b>111</b> |

| 6.6 Typical Characteristics.....               | 12         | <b>12 Device and Documentation Support</b> .....                           | <b>112</b> |

| <b>7 Detailed Description</b> .....            | <b>14</b>  | 12.1 Related Documentation.....                                            | <b>112</b> |

| 7.1 Overview.....                              | 14         | 12.2 Receiving Notification of Documentation Updates                       | <b>112</b> |

| 7.2 Functional Block Diagram.....              | 15         | 12.3 Support Resources.....                                                | <b>112</b> |

| 7.3 Feature Description.....                   | 17         | 12.4 Trademarks.....                                                       | <b>112</b> |

| 7.4 Programming.....                           | 68         | 12.5 Electrostatic Discharge Caution.....                                  | <b>112</b> |

| 7.5 Register Maps.....                         | 72         | 12.6 Glossary.....                                                         | <b>112</b> |

| <b>8 Application and Implementation</b> .....  | <b>101</b> | <b>13 Mechanical, Packaging, and Orderable</b><br><b>Information</b> ..... | <b>113</b> |

| 8.1 Application Information.....               | 101        |                                                                            |            |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| <b>Changes from Revision * (August 2022) to Revision A (December 2022)</b> | <b>Page</b> |

|----------------------------------------------------------------------------|-------------|

| • Updated device status to "Production Data" from "Advanced Information."  | <b>1</b>    |

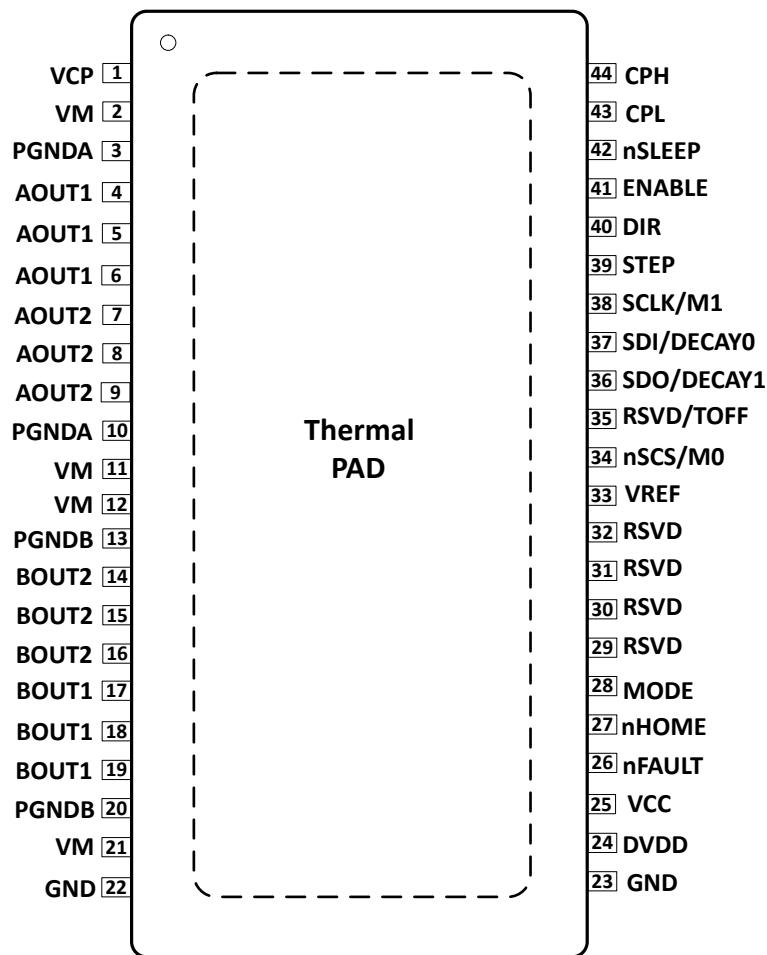

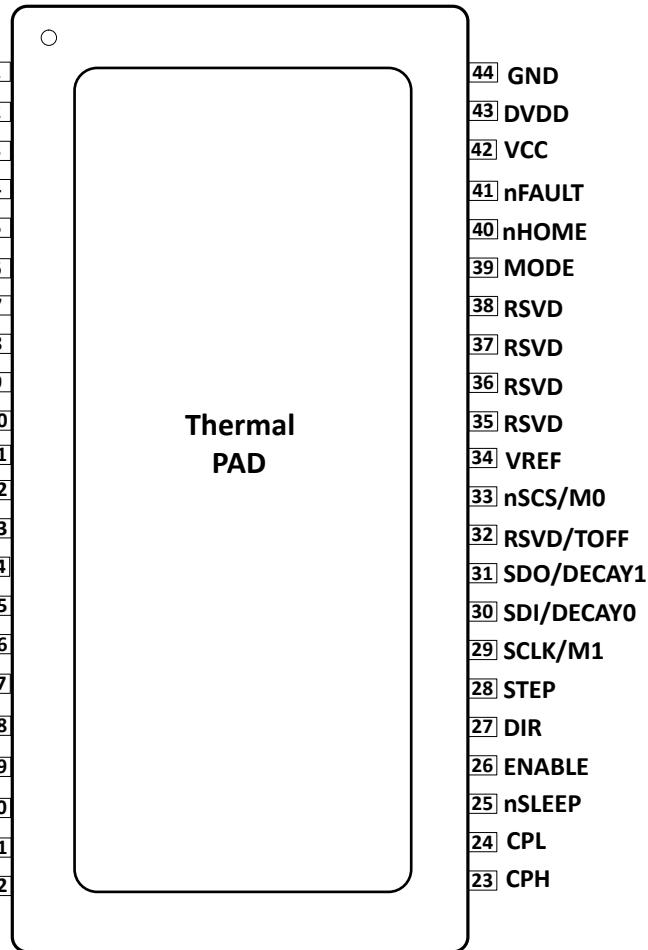

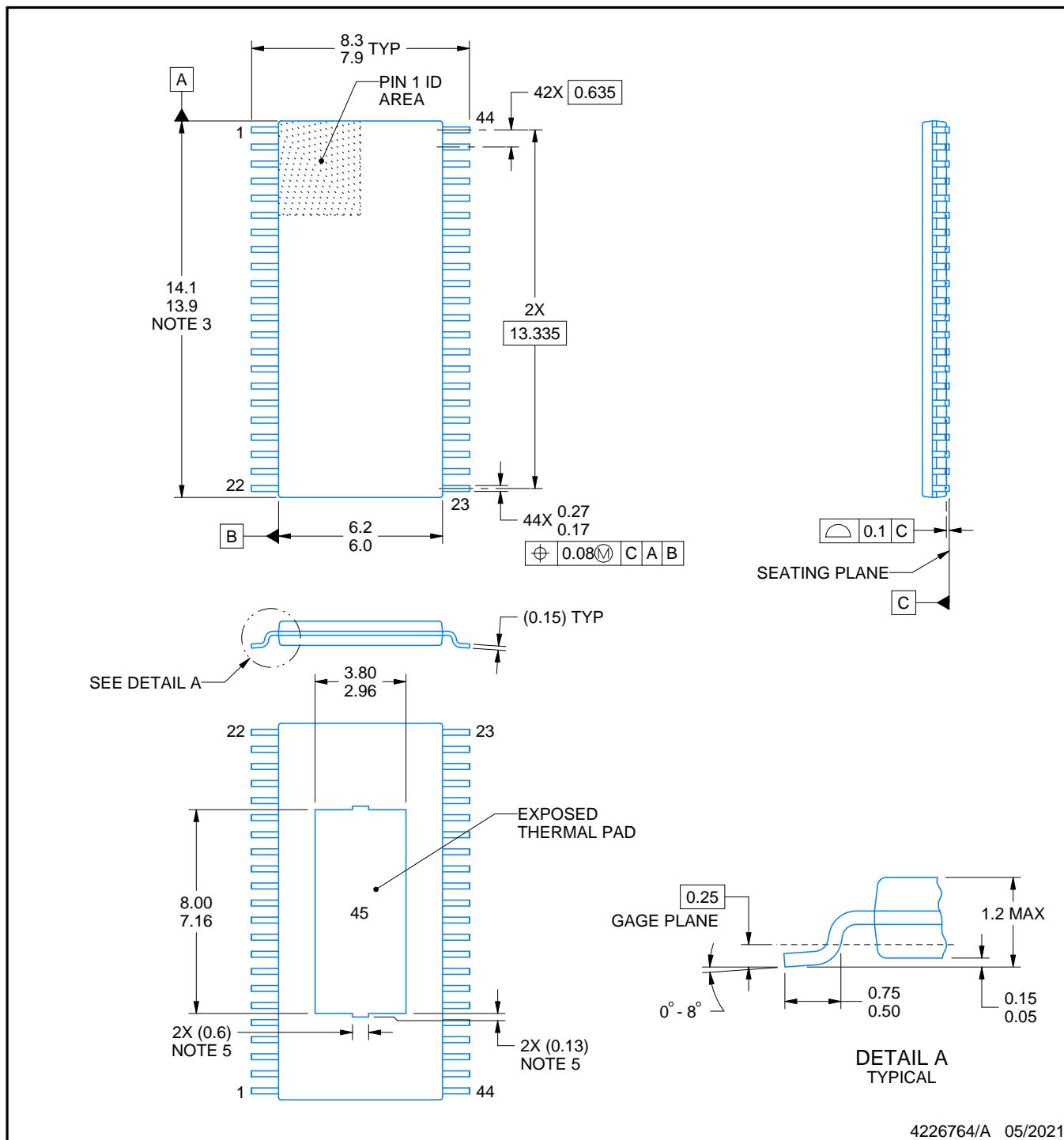

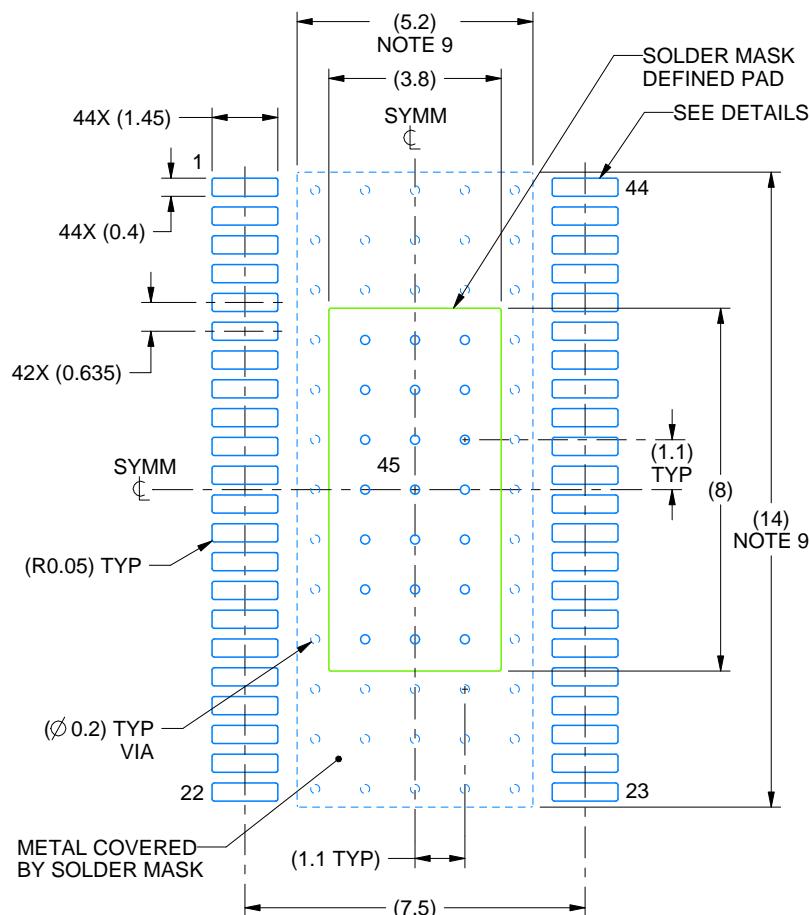

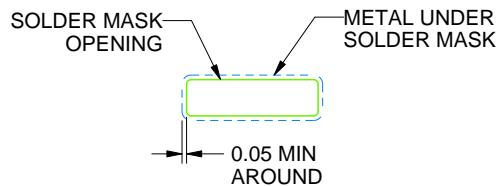

## 5 Pin Configuration and Functions

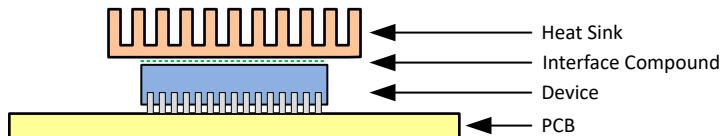

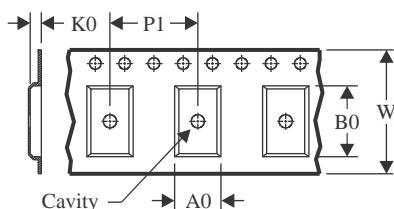

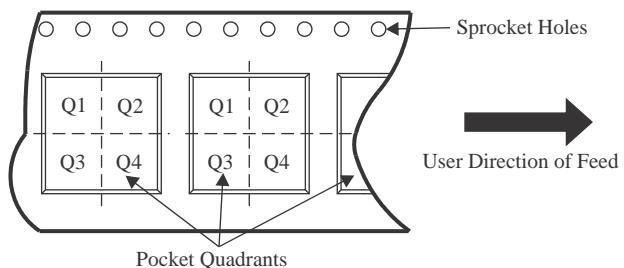

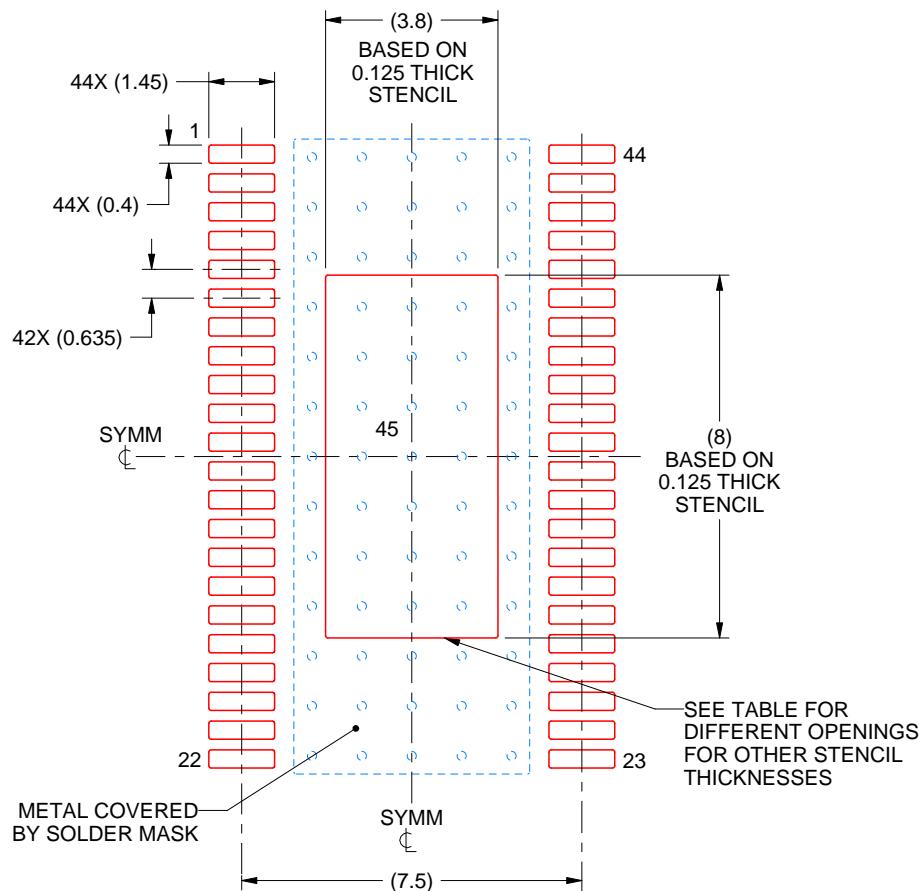

The DRV8462 is available in thermally-enhanced, 44-Pin HTSSOP packages.

- The DDW package contains a PowerPAD™ on the bottom side of the device.

- The DDV package contains a PowerPAD™ on the top side of the device for thermal coupling to a heatsink.

Figure 5-1. DDW Package (44-Pin HTSSOP), Top View

Figure 5-2. DDV Package (44-Pin HTSSOP), Top View

| PIN   |               |               | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                                 |

|-------|---------------|---------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | DDW           | DDV           |        |                                                                                                                                                                                                                                                                             |

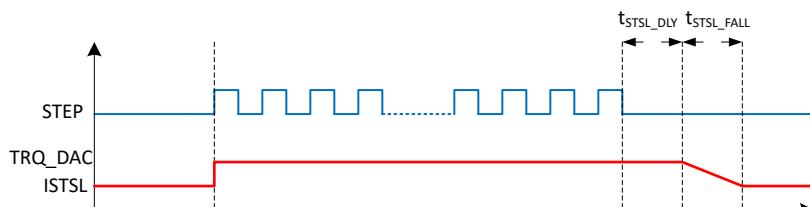

| VCP   | 1             | 22            | Power  | Charge pump output. Connect a X7R, 1- $\mu$ F, 16-V ceramic capacitor from VCP to VM.                                                                                                                                                                                       |

| VM    | 2, 11, 12, 21 | 2, 11, 12, 21 | Power  | Power supply. Connect to motor supply voltage and bypass to PGNDA and PGNDB with two 0.01- $\mu$ F ceramic capacitors (one for each pair of pins) plus a bulk capacitor rated for VM.                                                                                       |

| PGNDA | 3, 10         | 13, 20        | Power  | Power ground. Connect to system ground.                                                                                                                                                                                                                                     |

| PGNDB | 13, 20        | 3, 10         | Power  | Power ground. Connect to system ground.                                                                                                                                                                                                                                     |

| AOUT1 | 4, 5, 6       | 17, 18, 19    | Output | Winding A output. Connect to motor winding.                                                                                                                                                                                                                                 |

| AOUT2 | 7, 8, 9       | 14, 15, 16    | Output | Winding A output. Connect to motor winding.                                                                                                                                                                                                                                 |

| BOUT2 | 14, 15, 16    | 7, 8, 9       | Output | Winding B output. Connect to motor winding.                                                                                                                                                                                                                                 |

| BOUT1 | 17, 18, 19    | 4, 5, 6       | Output | Winding B output. Connect to motor winding.                                                                                                                                                                                                                                 |

| GND   | 22, 23        | 1, 44         | Power  | Device ground. Connect to system ground.                                                                                                                                                                                                                                    |

| DVDD  | 24            | 43            | Power  | Internal LDO output. Connect a X7R, 1- $\mu$ F, 6.3-V or 10-V rated ceramic capacitor to GND.                                                                                                                                                                               |

| VCC   | 25            | 42            | Power  | Supply voltage for internal logic blocks. When separate logic supply voltage is not available, tie the VCC pin to the DVDD pin. When configured with SPI interface, the VCC pin also acts as the supply pin for SDO output. See <a href="#">Section 7.3.17</a> for details. |

| PIN        |                |                | TYPE            | DESCRIPTION                                                                                                                                                                                                                        |

|------------|----------------|----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | DDW            | DDV            |                 |                                                                                                                                                                                                                                    |

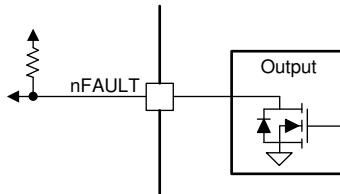

| nFAULT     | 26             | 41             | Open Drain      | Fault indication output. Pulled logic low with fault condition. Open-drain nFAULT requires an external pullup resistor.                                                                                                            |

| nHOME      | 27             | 40             | Open Drain      | Pulled logic low when the internal indexer is at home position (45°) of step table. The nHOME pin outputs one low pulse per 360° electrical rotation (four fullsteps). See <a href="#">Section 7.3.5.1</a> for details.            |

| MODE       | 28             | 39             | Input           | MODE pin programs the device to operate with either SPI or hardware (H/W) pin interface. See <a href="#">Section 7.3.1</a> for details.                                                                                            |

| RSVD       | 29, 30, 31, 32 | 35, 36, 37, 38 | -               | Reserved. Leave unconnected.                                                                                                                                                                                                       |

| VREF       | 33             | 34             | Input           | Voltage reference input for setting full-scale current. DVDD can be used to generate VREF through a resistor divider. When configured with SPI interface, the VREF pin can be left unconnected if VREF_INT_EN bit is 1b.           |

| nSCS/M0    | 34             | 33             | Input           | With SPI interface, this pin acts as serial chip select. An active low on this pin enables the serial interface communications. With H/W interface, this pin programs the microstepping mode.                                      |

| RSVD/TOFF  | 35             | 32             | Input           | This pin is not used with SPI interface. With H/W interface, this pin programs the OFF time for PWM current regulation.                                                                                                            |

| SDO/DECAY1 | 36             | 31             | Push-Pull/Input | With SPI interface, this pin acts as serial data output. Data is shifted out on the rising edge of the SCLK pin. With H/W interface, this pin programs the decay-mode.                                                             |

| SDI/DECAY0 | 37             | 30             | Input           | With SPI interface, this pin acts as serial data input. Data is captured on the falling edge of the SCLK pin. With H/W interface, this pin programs the decay-mode.                                                                |

| SCLK/M1    | 38             | 29             | Input           | With SPI interface, this pin acts as serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin. With H/W interface, this pin programs the microstepping mode.           |

| STEP       | 39             | 28             | Input           | Step input. An active edge causes the indexer to advance one step. With SPI interface, STEP active edge can be either rising edge or both rising and falling edge. With H/W interface, STEP active edge is always the rising edge. |

| DIR        | 40             | 27             | Input           | Direction input. Logic level sets the direction of stepping.                                                                                                                                                                       |

| ENABLE     | 41             | 26             | Input           | Logic low to disable device outputs; logic high to enable. When the device operates with H/W interface, the ENABLE pin also determines the OCP, OL and OTSD fault recovery methods.                                                |

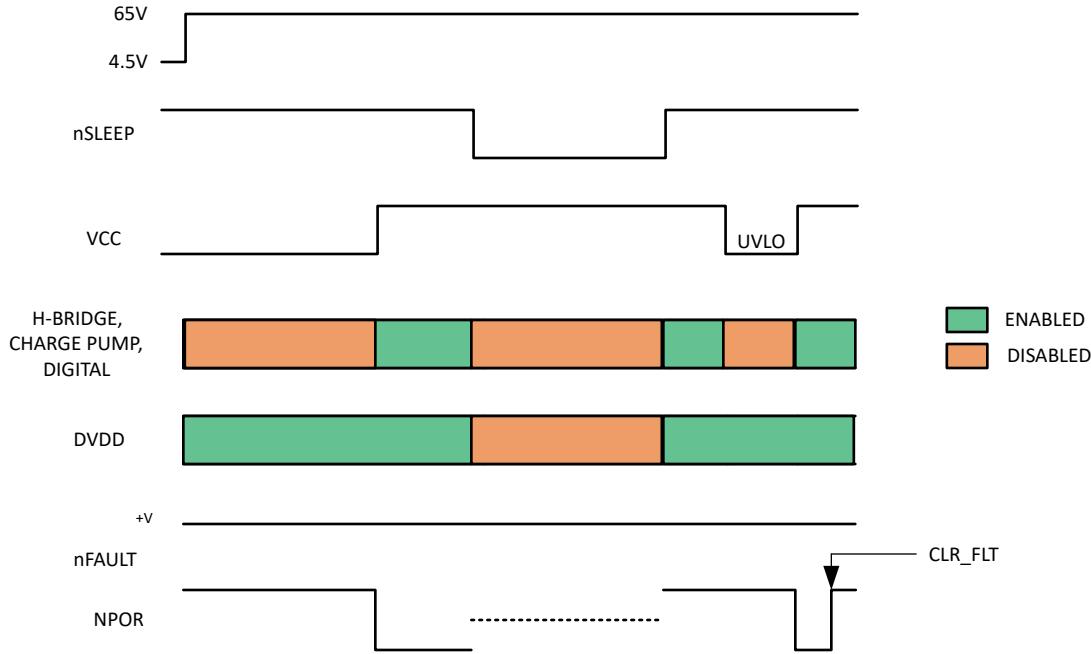

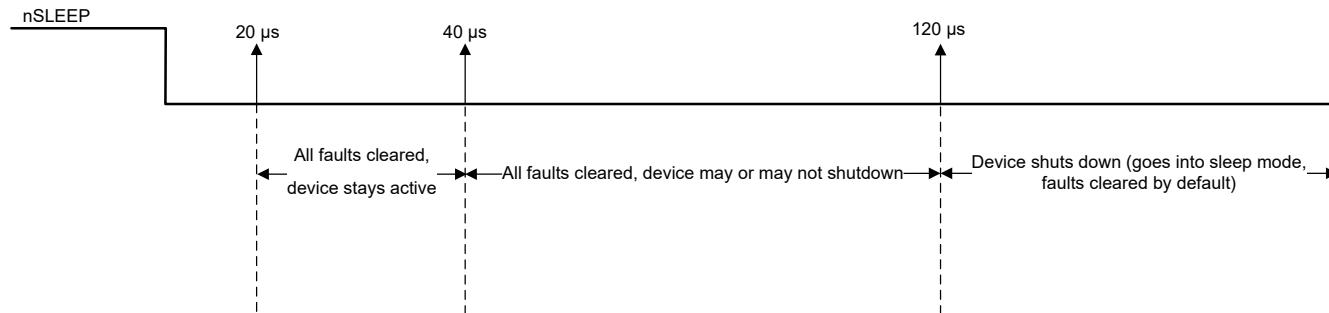

| nSLEEP     | 42             | 25             | Input           | Sleep mode input. Logic high to enable device; logic low to enter low-power sleep mode. A narrow nSLEEP reset pulse clears latched faults.                                                                                         |

| CPL        | 43             | 24             | Power           | Charge pump switching node. Connect a X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor from CPH to CPL.                                                                                                                               |

| CPH        | 44             | 23             | Power           |                                                                                                                                                                                                                                    |

| PAD        | -              | -              | -               | Thermal pad. Connect to system ground.                                                                                                                                                                                             |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted).<sup>(1)(2)</sup>

|                                                                  | MIN                | MAX             | UNIT |

|------------------------------------------------------------------|--------------------|-----------------|------|

| Power supply voltage (VM)                                        | -0.3               | 70              | V    |

| Charge pump voltage (VCP, CPH)                                   | -0.3               | $V_{VM} + 5.75$ | V    |

| Charge pump negative switching pin (CPL)                         | -0.3               | $V_{VM}$        | V    |

| nSLEEP pin voltage (nSLEEP)                                      | -0.3               | $V_{VM}$        | V    |

| Internal regulator voltage (DVDD)                                | -0.3               | 5.75            | V    |

| External logic supply (VCC)                                      | -0.3               | 5.75            | V    |

| Control pin voltage                                              | -0.3               | 5.75            | V    |

| Reference input pin voltage (VREF)                               | -0.3               | 5.75            | V    |

| PGND <sub>x</sub> to GND voltage                                 | -0.5               | 0.5             | V    |

| PGND <sub>x</sub> to GND voltage, < 1 $\mu$ s                    | -2.5               | 2.5             | V    |

| Open drain output current (nFAULT, nHOME)                        | 0                  | 10              | mA   |

| Continuous Output pin voltage (AOUT1, AOUT2, BOUT1, BOUT2)       | -1                 | $V_{VM} + 1$    | V    |

| Transient 100 ns Output pin voltage (AOUT1, AOUT2, BOUT1, BOUT2) | -3                 | $V_{VM} + 3$    | V    |

| Peak drive current (AOUT1, AOUT2, BOUT1, BOUT2)                  | Internally Limited |                 | A    |

| Operating ambient temperature, $T_A$                             | -40                | 125             | °C   |

| Operating junction temperature, $T_J$                            | -40                | 150             | °C   |

| Storage temperature, $T_{stg}$                                   | -65                | 150             | °C   |

1. *Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.*

2. *All voltage values are with respect to network ground terminal GND.*

### 6.2 ESD Ratings

|             |                         |                                                                       | VALUE                                               | UNIT |

|-------------|-------------------------|-----------------------------------------------------------------------|-----------------------------------------------------|------|

| $V_{(ESD)}$ | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | $\pm 2000$                                          | V    |

|             |                         | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | Corner Pins<br>$\pm 750$<br>Other Pins<br>$\pm 500$ |      |

|             |                         |                                                                       |                                                     |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted).

|            |                                                   | MIN  | MAX                | UNIT |

|------------|---------------------------------------------------|------|--------------------|------|

| $V_{VM}$   | Supply voltage range for normal (DC) operation    | 4.5  | 65                 | V    |

| $V_I$      | Logic level input voltage                         | 0    | 5.5                | V    |

| $V_{VCC}$  | VCC pin voltage                                   | 3.05 | 5.5                | V    |

| $V_{REF}$  | Reference voltage (VREF)                          | 0.05 | 3.3                | V    |

| $f_{STEP}$ | Applied STEP signal (STEP)                        | 0    | 100 <sup>(1)</sup> | kHz  |

| $I_{FS}$   | Motor full-scale current with DDW package (xOUTx) | 0    | 5 <sup>(2)</sup>   | A    |

## 6.3 Recommended Operating Conditions (continued)

Over operating free-air temperature range (unless otherwise noted).

|           |                                                   | MIN | MAX                | UNIT |

|-----------|---------------------------------------------------|-----|--------------------|------|

| $I_{FS}$  | Motor full-scale current with DDV package (xOUTx) | 0   | 10 <sup>(2)</sup>  | A    |

| $I_{RMS}$ | Motor RMS current with DDW package (xOUTx)        | 0   | 3.5 <sup>(2)</sup> | A    |

| $I_{RMS}$ | Motor RMS current with DDV package (xOUTx)        | 0   | 7 <sup>(2)</sup>   | A    |

| $T_A$     | Operating ambient temperature                     | -40 | 125                | °C   |

| $T_J$     | Operating junction temperature                    | -40 | 150                | °C   |

1. *STEP input can operate up to 500 kHz, but system bandwidth is limited by the motor load.*

2. *Power dissipation and thermal limits must be observed.*

## 6.4 Thermal Information

| THERMAL METRIC       |                                              | DDW  | DDV  | UNIT |

|----------------------|----------------------------------------------|------|------|------|

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 22.2 | 44.2 | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 9.1  | 0.7  | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 5.3  | 18.9 | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 0.1  | 0.3  | °C/W |

| $\Psi_{JB}$          | Junction-to-board characterization parameter | 5.3  | 18.6 | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.7  | N/A  | °C/W |

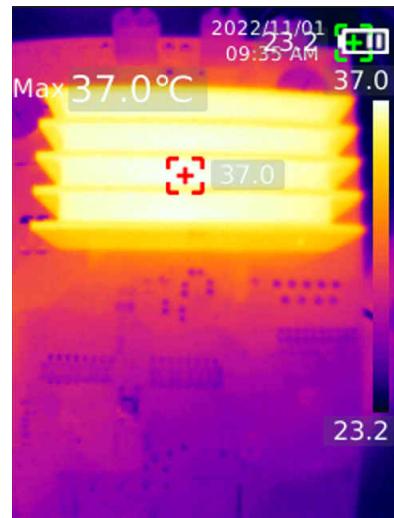

For the DDV package, as the exposed pad is on top of the package,  $R_{\theta JC(top)}$  is the most important thermal resistance parameter.

## 6.5 Electrical Characteristics

Typical values are at  $T_A = 25^\circ\text{C}$  and  $V_{VM} = 24\text{ V}$ . All limits are over recommended operating conditions, unless otherwise noted.

| PARAMETER                                                                    | TEST CONDITIONS                                                                     | MIN                                                      | TYP  | MAX          | UNIT                    |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------|------|--------------|-------------------------|

| <b>POWER SUPPLIES (VM, DVDD)</b>                                             |                                                                                     |                                                          |      |              |                         |

| $I_{VM}$                                                                     | VM operating supply current                                                         | ENABLE = 1, nSLEEP = 1, No motor load, VCC = External 5V |      | 5            | 8                       |

|                                                                              |                                                                                     | ENABLE = 1, nSLEEP = 1, No motor load, VCC = DVDD        |      | 8.5          | 11                      |

| $I_{VMQ}$                                                                    | VM sleep mode supply current                                                        | nSLEEP = 0                                               |      | 3            | $\mu\text{A}$           |

| $t_{SLEEP}$                                                                  | Sleep time                                                                          | nSLEEP = 0 to sleep-mode                                 | 120  |              | $\mu\text{s}$           |

| $t_{RESET}$                                                                  | nSLEEP reset pulse                                                                  | nSLEEP low to clear fault                                | 20   |              | $\mu\text{s}$           |

| $t_{WAKE}$                                                                   | Wake-up time                                                                        | H/W interface, nSLEEP = 1 to output transition           |      | 0.85         | 1.2                     |

|                                                                              |                                                                                     | SPI interface, nSLEEP = 1 to SPI ready                   |      | 0.16         | 0.25                    |

| $t_{ON}$                                                                     | Turn-on time <sup>(1)</sup>                                                         | VM > UVLO to output transition                           |      | 1            | 1.3                     |

| $V_{DVDD}$                                                                   | Internal regulator voltage                                                          | No external load, 6 V < $V_{VM}$ < 65 V                  | 4.75 | 5            | 5.25                    |

|                                                                              |                                                                                     | No external load, $V_{VM} = 4.5\text{ V}$                | 4.2  | 4.35         |                         |

| <b>CHARGE PUMP (VCP, CPH, CPL)</b>                                           |                                                                                     |                                                          |      |              |                         |

| $V_{VCP}$                                                                    | VCP operating voltage                                                               | 6 V < $V_{VM}$ < 65 V                                    |      | $V_{VM} + 5$ |                         |

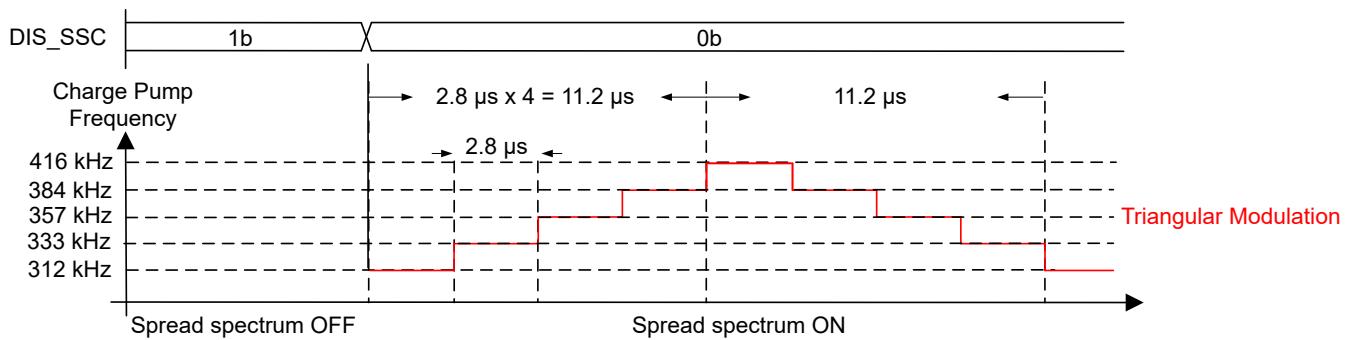

| $f_{VCP}$                                                                    | Charge pump switching frequency                                                     | $V_{VM} > \text{UVLO}$ ; nSLEEP = 1                      |      | 357          | $\text{kHz}$            |

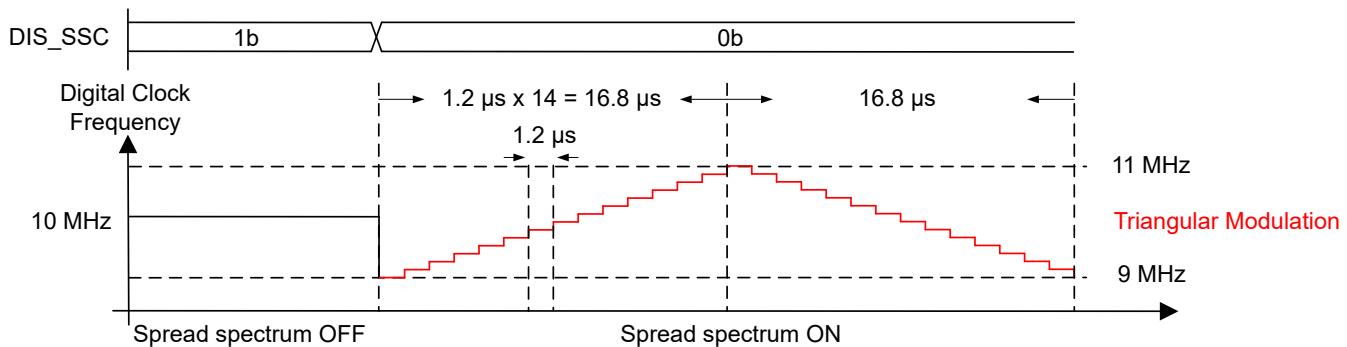

| $f_{CLK}$                                                                    | Internal digital clock frequency                                                    | $V_{VM} > \text{UVLO}$ ; nSLEEP = 1                      |      | 10           | $\text{MHz}$            |

| <b>LOGIC-LEVEL INPUTS (STEP, DIR, MODE, DECAY1, nSCS, SCLK, SDI, nSLEEP)</b> |                                                                                     |                                                          |      |              |                         |

| $V_{IL}$                                                                     | Input logic-low voltage                                                             |                                                          | 0    |              | $0.6\text{ V}$          |

| $V_{IH}$                                                                     | Input logic-high voltage (all pins except DECAY1)                                   |                                                          | 1.5  |              | $5.5\text{ V}$          |

| $V_{IH\_DECAY1}$                                                             | Input logic-high voltage (DECAY1 pin)                                               |                                                          | 2.7  |              | $5.5\text{ V}$          |

| $V_{HYS}$                                                                    | Input logic hysteresis (all pins except nSLEEP)                                     |                                                          |      | 100          | $\text{mV}$             |

| $V_{HYS\_SLEEP}$                                                             | nSLEEP logic hysteresis                                                             |                                                          |      | 300          | $\text{mV}$             |

| $I_{IL}$                                                                     | Input logic-low current (all pins except nSCS)                                      | $V_{IN} = 0\text{ V}$                                    | -1   |              | $1\text{ }\mu\text{A}$  |

| $I_{IL\_nSCS}$                                                               | nSCS logic-low current                                                              | $nSCS = 0\text{V}$                                       | 8    |              | $12\text{ }\mu\text{A}$ |

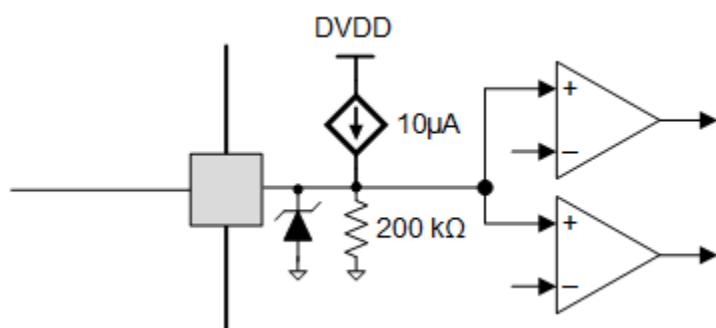

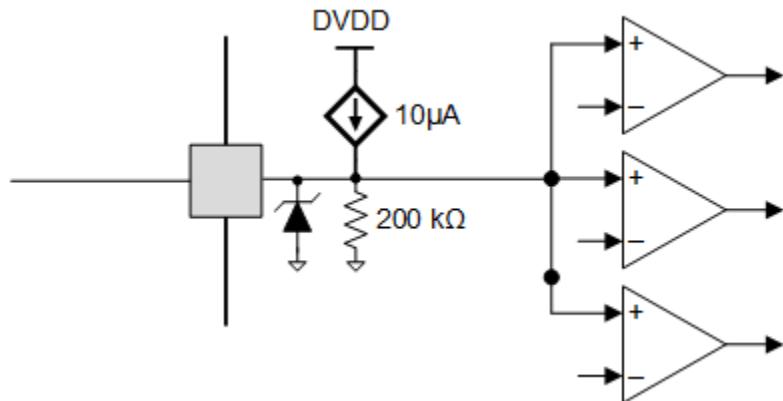

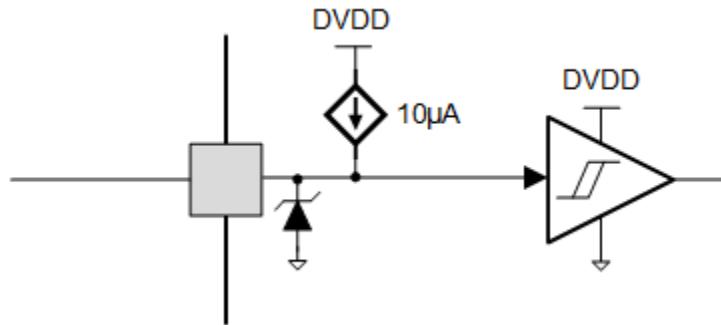

| $I_{IH}$                                                                     | Input logic-high current (all pins except nSCS, 200k internal pull-down resistance) | $V_{IN} = \text{DVDD}$                                   |      | 50           | $\mu\text{A}$           |

| $I_{IH\_nSCS}$                                                               | nSCS logic-high current                                                             | $nSCS = \text{DVDD}$                                     |      | 0.1          | $\mu\text{A}$           |

| <b>TRI-LEVEL INPUTS (M0, DECAY0, ENABLE)</b>                                 |                                                                                     |                                                          |      |              |                         |

| $V_{I1\_tri}$                                                                | Input logic-low voltage                                                             | Tied to GND                                              | 0    |              | $0.6\text{ V}$          |

| $V_{I2\_tri}$                                                                | Input Hi-Z voltage                                                                  | Hi-Z                                                     | 1.8  | 2            | $2.2\text{ V}$          |

| $V_{I3\_tri}$                                                                | Input logic-high voltage                                                            | Tied to DVDD                                             | 2.7  |              | $5.5\text{ V}$          |

| $I_{O\_tri}$                                                                 | Output pull-up current                                                              |                                                          |      | 10.5         | $\mu\text{A}$           |

| <b>QUAD-LEVEL INPUTS (M1, TOFF)</b>                                          |                                                                                     |                                                          |      |              |                         |

| $V_{I1\_quad}$                                                               | Input logic-low voltage                                                             | Tied to GND                                              | 0    |              | $0.6\text{ V}$          |

Typical values are at  $T_A = 25^\circ\text{C}$  and  $V_{VM} = 24\text{ V}$ . All limits are over recommended operating conditions, unless otherwise noted.

| PARAMETER                                                |                                                                 | TEST CONDITIONS                                                  | MIN   | TYP  | MAX   | UNIT             |

|----------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|-------|------|-------|------------------|

| $V_{I2\_quad}$                                           | Input second level voltage                                      | $330\text{k}\Omega \pm 5\%$ to GND                               | 1     | 1.25 | 1.4   | V                |

| $V_{I3\_quad}$                                           | Input Hi-Z voltage                                              | Hi-Z                                                             | 1.8   | 2    | 2.2   | V                |

| $V_{I4\_quad}$                                           | Input logic-high voltage                                        | Tied to DVDD                                                     | 2.7   |      | 5.5   | V                |

| $I_{O\_quad}$                                            | Output pull-up current                                          |                                                                  |       | 10.5 |       | $\mu\text{A}$    |

| <b>PUSH-PULL OUTPUT (SDO)</b>                            |                                                                 |                                                                  |       |      |       |                  |

| $R_{PD,SDO}$                                             | Internal pull-down resistance                                   | 5mA load, with respect to GND                                    |       | 30   | 60    | $\Omega$         |

| $R_{PU,SDO}$                                             | Internal pull-up resistance                                     | 5mA load, with respect to VCC                                    |       | 60   | 110   | $\Omega$         |

| $I_{SDO}$                                                | SDO Leakage Current <sup>(1)</sup>                              | $V_{VM} > 6\text{ V}$ , SDO = VCC and 0V                         | -2.5  |      | 2.5   | $\mu\text{A}$    |

| <b>CONTROL OUTPUTS (nFAULT, nHOME)</b>                   |                                                                 |                                                                  |       |      |       |                  |

| $V_{OL}$                                                 | Output logic-low voltage                                        | $I_O = 5\text{ mA}$                                              |       |      | 0.35  | V                |

| $I_{OH}$                                                 | Output logic-high leakage                                       |                                                                  | -1    |      | 1     | $\mu\text{A}$    |

| <b>MOTOR DRIVER OUTPUTS (AOUT1, AOUT2, BOUT1, BOUT2)</b> |                                                                 |                                                                  |       |      |       |                  |

| $R_{DS(ONH)}$                                            | High-side FET on resistance                                     | $T_J = 25^\circ\text{C}$ , $I_O = -5\text{ A}$                   |       | 50   | 60    | $\text{m}\Omega$ |

|                                                          |                                                                 | $T_J = 125^\circ\text{C}$ , $I_O = -5\text{ A}$                  |       | 75   | 94    | $\text{m}\Omega$ |

|                                                          |                                                                 | $T_J = 150^\circ\text{C}$ , $I_O = -5\text{ A}$                  |       | 85   | 107   | $\text{m}\Omega$ |

| $R_{DS(ONL)}$                                            | Low-side FET on resistance                                      | $T_J = 25^\circ\text{C}$ , $I_O = 5\text{ A}$                    |       | 46   | 55    | $\text{m}\Omega$ |

|                                                          |                                                                 | $T_J = 125^\circ\text{C}$ , $I_O = 5\text{ A}$                   |       | 68   | 90    | $\text{m}\Omega$ |

|                                                          |                                                                 | $T_J = 150^\circ\text{C}$ , $I_O = 5\text{ A}$                   |       | 75   | 100   | $\text{m}\Omega$ |

| $I_{LEAK}$                                               | Output leakage current to ground in Disable mode <sup>(1)</sup> | H-bridges are Hi-Z, $V_{VM} = 65\text{ V}$                       |       |      | 200   | $\mu\text{A}$    |

| $t_{RF}$                                                 | Output rise/fall time                                           | H/W interface, $I_O = 5\text{ A}$ , between 10% and 90%          |       | 140  |       | ns               |

|                                                          |                                                                 | SPI interface, SR = 0b, $I_O = 5\text{ A}$ , between 10% and 90% |       | 140  |       |                  |

|                                                          |                                                                 | SPI interface, SR = 1b, $I_O = 5\text{ A}$ , between 10% and 90% |       | 70   |       |                  |

| $t_D$                                                    | Output dead time                                                | $VM = 24\text{V}$ , $I_O = 5\text{ A}$                           |       | 300  |       | ns               |

| <b>PWM CURRENT CONTROL (VREF)</b>                        |                                                                 |                                                                  |       |      |       |                  |

| $K_V$                                                    | Transimpedance gain                                             | VREF = 3.3 V, DDW Package                                        | 0.625 | 0.66 | 0.695 | V/A              |

|                                                          |                                                                 | VREF = 3.3 V, DDV Package                                        | 0.313 | 0.33 | 0.347 |                  |

| $I_{VREF}$                                               | VREF Pin Leakage Current                                        | VREF = 3.3 V                                                     |       |      | 20    | nA               |

| $t_{OFF}$                                                | PWM off-time                                                    | TOFF = 0 or TOFF = 00b                                           |       | 9    |       | $\mu\text{s}$    |

|                                                          |                                                                 | TOFF = 1 or TOFF = 01b                                           |       | 19   |       |                  |

|                                                          |                                                                 | TOFF = Hi-Z or TOFF = 10b                                        |       | 27   |       |                  |

|                                                          |                                                                 | TOFF = $330\text{k}\Omega$ to GND or TOFF = 11b                  |       | 35   |       |                  |

| $\Delta I_{TRIP\_EXT}$                                   | Current trip accuracy, external VREF input                      | 10% to 20% full-scale current                                    | -12   |      | 12    | %                |

|                                                          |                                                                 | 20% to 40% full-scale current                                    | -8    |      | 5     |                  |

|                                                          |                                                                 | 40% to 100% full-scale current                                   | -5    |      | 4     |                  |

| $\Delta I_{TRIP\_INT}$                                   | Current trip accuracy, internal VREF                            | 10% to 20% full-scale current                                    | -12   |      | 12    | %                |

|                                                          |                                                                 | 20% to 40% full-scale current                                    | -9    |      | 6     |                  |

|                                                          |                                                                 | 40% to 100% full-scale current                                   | -6    |      | 5     |                  |

Typical values are at  $T_A = 25^\circ\text{C}$  and  $V_{VM} = 24\text{ V}$ . All limits are over recommended operating conditions, unless otherwise noted.

| PARAMETER                  |                                    | TEST CONDITIONS                                                            | MIN  | TYP          | MAX  | UNIT             |

|----------------------------|------------------------------------|----------------------------------------------------------------------------|------|--------------|------|------------------|

| $I_{O,CH}$                 | AOUT and BOUT current matching     | 100% full-scale current                                                    | -2.5 |              | 2.5  | %                |

| $t_{BLK}$                  | Current regulation blanking time   | SPI interface, $TBLANK\_TIME = 00\text{b}$                                 |      | 1            |      | $\mu\text{s}$    |

|                            |                                    | H/W interface or SPI interface, $TBLANK\_TIME = 01\text{b}$                |      | 1.5          |      |                  |

|                            |                                    | SPI interface, $TBLANK\_TIME = 10\text{b}$                                 |      | 2            |      |                  |

|                            |                                    | SPI interface, $TBLANK\_TIME = 11\text{b}$                                 |      | 2.5          |      |                  |

| $t_{DEG}$                  | Current regulation deglitch time   |                                                                            |      | 0.5          |      | $\mu\text{s}$    |

| <b>PROTECTION CIRCUITS</b> |                                    |                                                                            |      |              |      |                  |

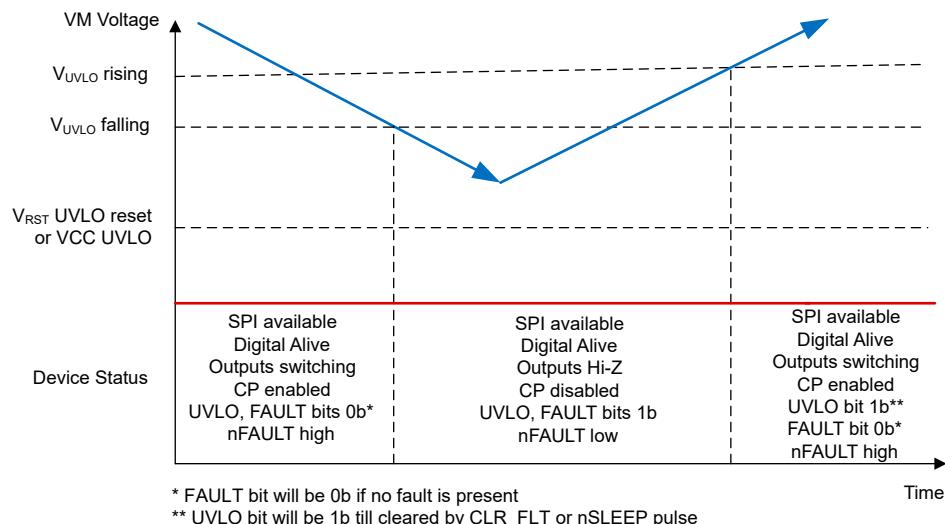

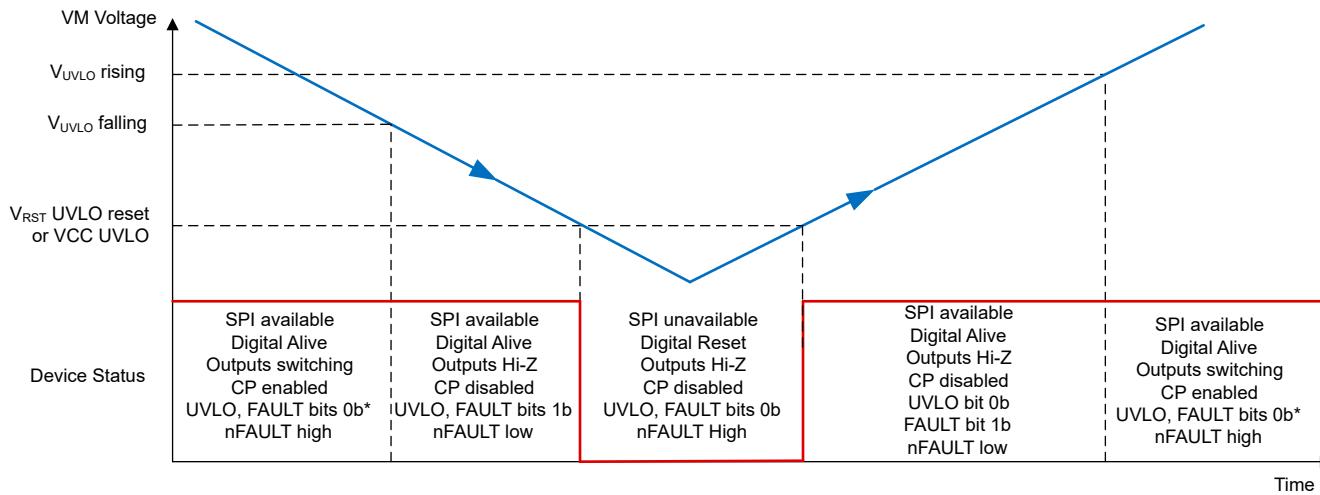

| $V_{M_{UVLO}}$             | VM UVLO lockout                    | VM falling                                                                 | 4.1  | 4.23         | 4.35 | V                |

|                            |                                    | VM rising                                                                  | 4.2  | 4.35         | 4.45 |                  |

| $V_{C_{UVLO}}$             | VCC UVLO lockout                   | VCC connected to external voltage, VCC falling                             | 2.7  | 2.8          | 2.9  | V                |

|                            |                                    | VCC connected to external voltage, VCC rising                              | 2.8  | 2.92         | 3.05 |                  |

| $V_{UVLO,HYS}$             | Undervoltage hysteresis            | Rising to falling threshold                                                |      | 120          |      | mV               |

| $V_{RST}$                  | VM UVLO reset                      | VCC = DVDD, SPI interface, VM falling, device reset, no SPI communications |      |              | 3.4  | V                |

| $V_{CPUV}$                 | Charge pump undervoltage           | VCP falling                                                                |      | $V_{VM} + 2$ |      | V                |

| $I_{OCP}$                  | Overcurrent protection             | Current through any FET, DDW Package                                       | 8    |              |      | A                |

|                            |                                    | Current through any FET, DDV Package                                       | 16   |              |      | A                |

| $t_{OCP}$                  | Overcurrent detection delay        | H/W Interface                                                              |      | 2.2          |      | $\mu\text{s}$    |

|                            |                                    | SPI Interface, $TOCP = 0\text{b}$                                          |      | 1.2          |      |                  |

|                            |                                    | SPI Interface, $TOCP = 1\text{b}$                                          |      | 2.2          |      |                  |

| $t_{RETRY}$                | Overcurrent retry time             |                                                                            |      | 4.1          |      | ms               |

| $t_{OL}$                   | Open load detection time           | H/W Interface                                                              |      |              | 60   | ms               |

|                            |                                    | SPI Interface, $OL\_T = 00\text{b}$                                        |      |              | 30   |                  |

|                            |                                    | SPI Interface, $OL\_T = 01\text{b}$                                        |      |              | 60   |                  |

|                            |                                    | SPI Interface, $OL\_T = 10\text{b}$                                        |      |              | 120  |                  |

| $I_{OL}$                   | Open load current threshold        |                                                                            |      | 190          |      | mA               |

| $T_{OTW}$                  | Overtemperature warning            | SPI Interface, Die temperature $T_J$                                       | 135  | 150          | 165  | $^\circ\text{C}$ |

| $T_{HYS\_OTW}$             | Overtemperature warning hysteresis | SPI Interface, Die temperature $T_J$                                       |      | 20           |      | $^\circ\text{C}$ |

| $T_{OTSD}$                 | Thermal shutdown                   | Die temperature $T_J$                                                      | 150  | 165          | 180  | $^\circ\text{C}$ |

| $T_{HYS\_OTSD}$            | Thermal shutdown hysteresis        | Die temperature $T_J$                                                      |      | 20           |      | $^\circ\text{C}$ |

(1) Guaranteed by design

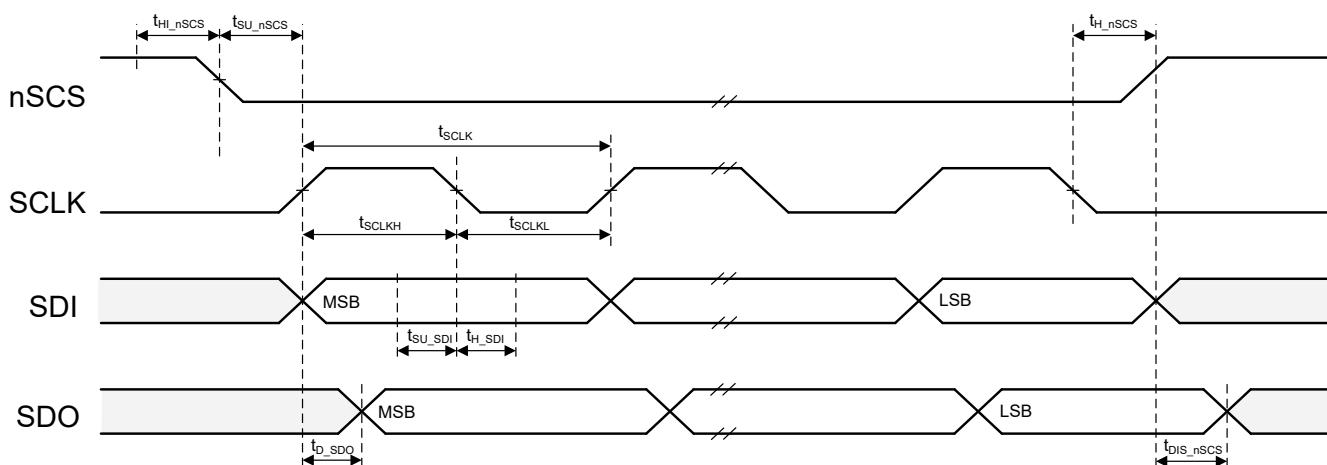

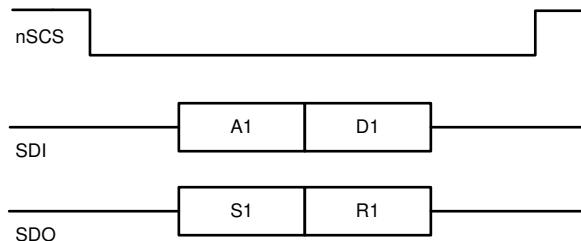

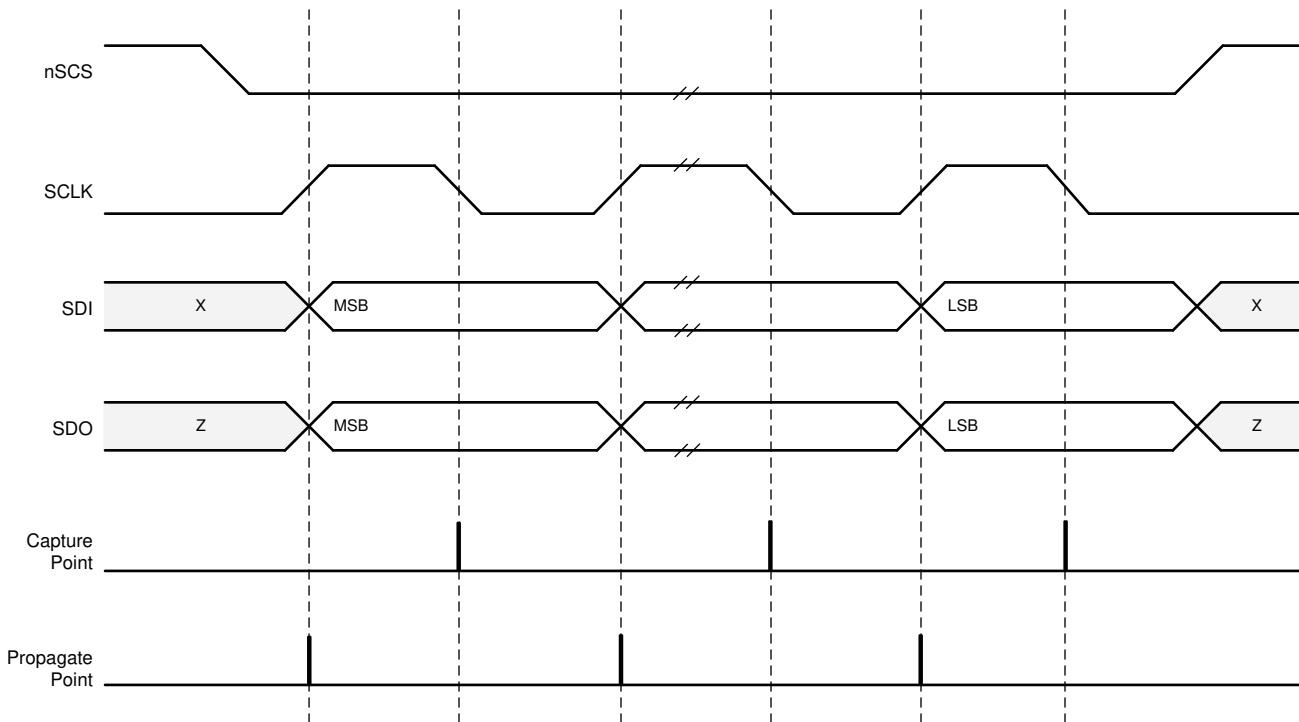

### 6.5.1 SPI Timing Requirements

|             |                           | MIN | NOM | MAX | UNIT |

|-------------|---------------------------|-----|-----|-----|------|

| $t_{READY}$ | SPI ready, $VM > V_{RST}$ |     | 1   |     | ms   |

|                 |                                                                      | MIN | NOM | MAX | UNIT          |

|-----------------|----------------------------------------------------------------------|-----|-----|-----|---------------|

| $t_{SCLK}$      | SCLK minimum period                                                  | 100 |     |     | ns            |

| $t_{SCLKH}$     | SCLK minimum high time                                               | 50  |     |     | ns            |

| $t_{SCLKL}$     | SCLK minimum low time                                                | 50  |     |     | ns            |

| $t_{SU\_SDI}$   | SDI input setup time                                                 | 20  |     |     | ns            |

| $t_{H\_SDI}$    | SDI input hold time                                                  | 30  |     |     | ns            |

| $t_{D\_SDO}$    | SDO output delay time, SCLK high to SDO valid, $C_L = 20 \text{ pF}$ |     |     | 30  | ns            |

| $t_{SU\_nSCS}$  | nSCS input setup time                                                | 50  |     |     | ns            |

| $t_{H\_nSCS}$   | nSCS input hold time                                                 | 50  |     |     | ns            |

| $t_{HI\_nSCS}$  | nSCS minimum high time before active low                             |     |     | 2   | $\mu\text{s}$ |

| $t_{DIS\_nSCS}$ | nSCS disable time, nSCS high to SDO high impedance                   |     | 10  |     | ns            |

**Figure 6-1. SPI Timing Diagram**

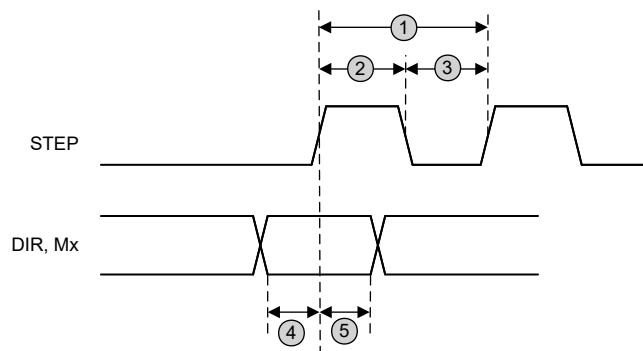

### 6.5.2 STEP and DIR Timing Requirements

Typical limits are at  $T_J = 25^\circ\text{C}$  and  $V_{VM} = 24 \text{ V}$ . Over recommended operating conditions unless otherwise noted.

| NO. |                   |                                      | MIN | MAX                | UNIT |

|-----|-------------------|--------------------------------------|-----|--------------------|------|

| 1   | $f_{STEP}$        | Step frequency                       |     | 500 <sup>(1)</sup> | kHz  |

| 2   | $t_{WH\_STEP}$    | Pulse duration, STEP high            | 970 |                    | ns   |

| 3   | $t_{WL\_STEP}$    | Pulse duration, STEP low             | 970 |                    | ns   |

| 4   | $t_{SU\_DIR, Mx}$ | Setup time, DIR or Mx to STEP rising | 200 |                    | ns   |

| 5   | $t_{H\_DIR, Mx}$  | Hold time, DIR or Mx to STEP rising  | 200 |                    | ns   |

(1) STEP input can operate up to 500 kHz, but system bandwidth is limited by the motor load.

**Figure 6-2. STEP and DIR Timing Diagram**

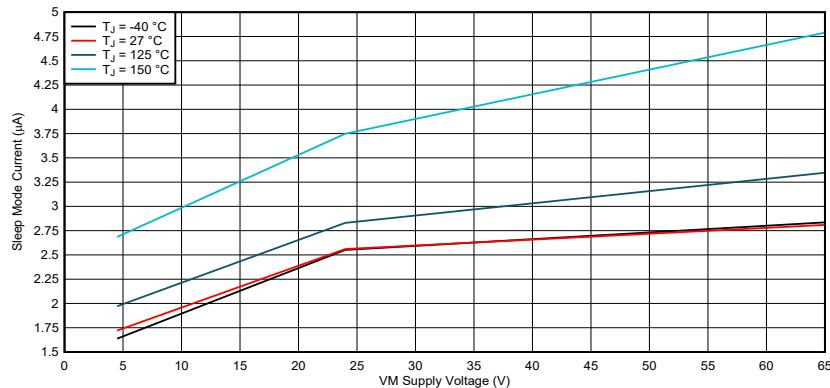

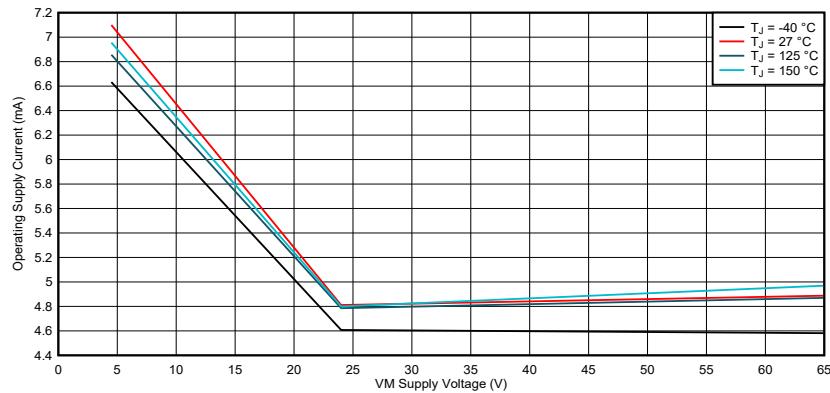

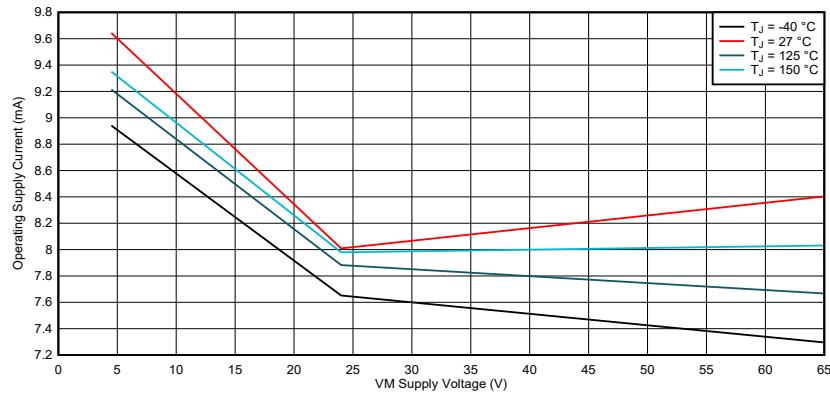

## 6.6 Typical Characteristics

Figure 6-3. Sleep mode supply current

Figure 6-4. Operating supply current,  $\text{VCC} = \text{External } 5\text{ V}$

Figure 6-5. Operating supply current,  $\text{VCC} = \text{DVDD}$

## 6.6 Typical Characteristics

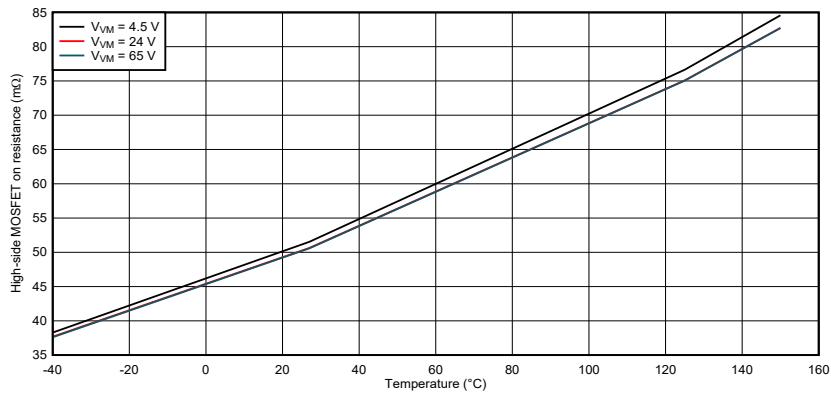

Figure 6-6. High-side FET on resistance

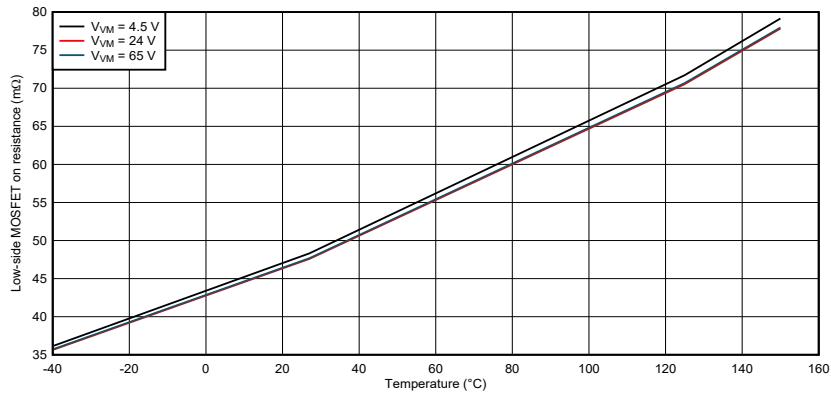

Figure 6-7. Low-side FET on resistance

## 7 Detailed Description

### 7.1 Overview

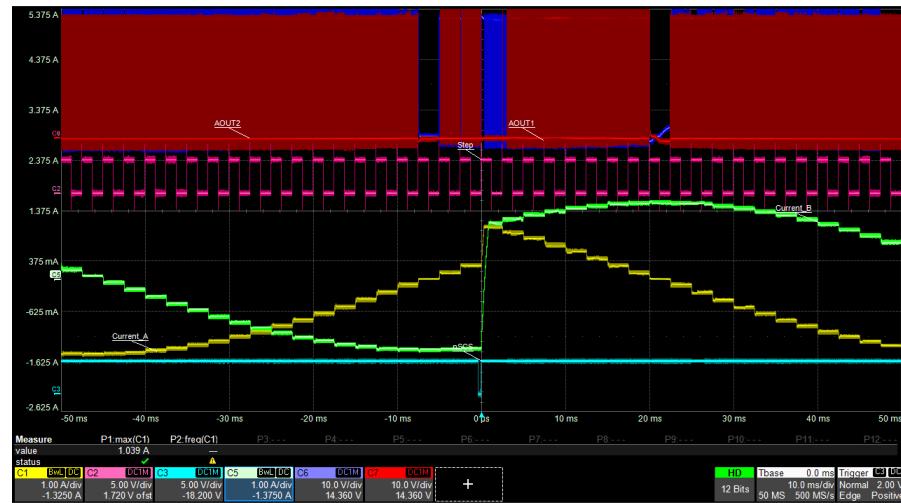

The DRV8462 is an integrated motor-driver solution for bipolar stepper motors. The device integrates two N-channel power MOSFET H-bridges, current sense resistors, current regulation circuitry, and a microstepping indexer. The DRV8462 is capable of supporting wide supply voltage of 4.5 V to 65 V. The device is available in two packages - a 44-pin HTSSOP (DDW) package with exposed pad at the bottom of the package; and another 44-pin HTSSOP (DDV) package with exposed pad on the top of the package. The DDW package provides an output current up to 8-A peak, 5-A full-scale, or 3.5-A root mean square (rms). When used with a low thermal resistance heat sink installed on the top of the DDV package, the DRV8462 can deliver an output current up to 16-A peak, 10-A full-scale, or 7-A root mean square (rms). The actual full-scale and rms current depends on the ambient temperature, supply voltage, and PCB thermal design. To provide scalable voltage and current solutions for the system design, the DRV8462 DDW package is pin-to-pin compatible with the [DRV8452](#), which is rated for 48 V maximum operating voltage and 5 A full-scale current; and the [DRV8461](#), which is rated for 65 V maximum operating voltage and 3 A full-scale current.

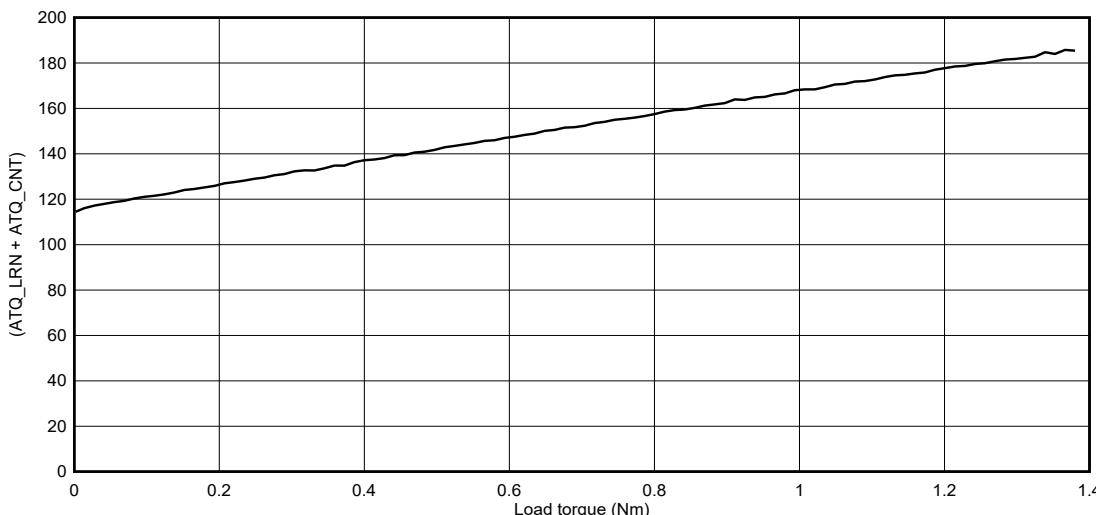

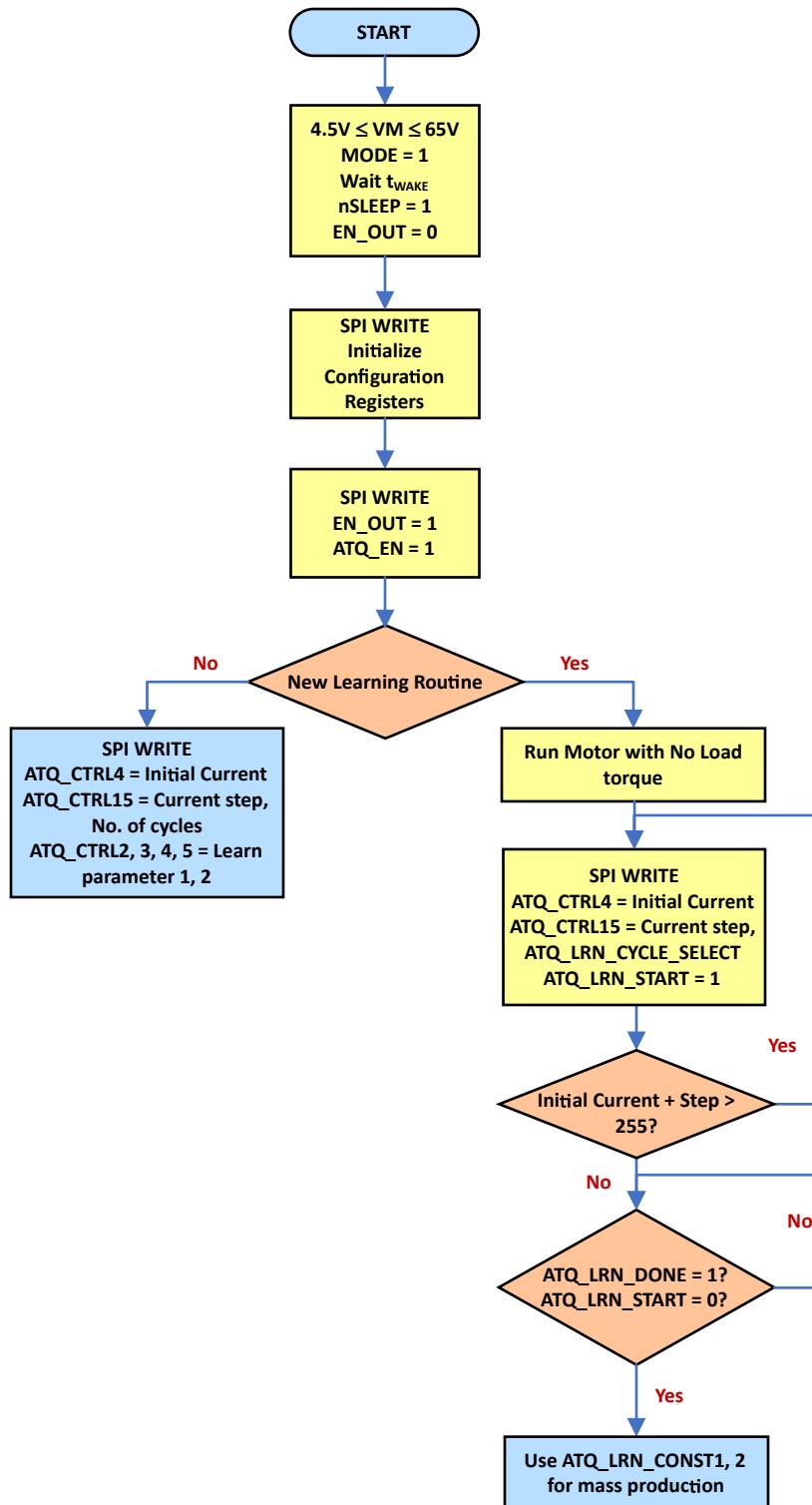

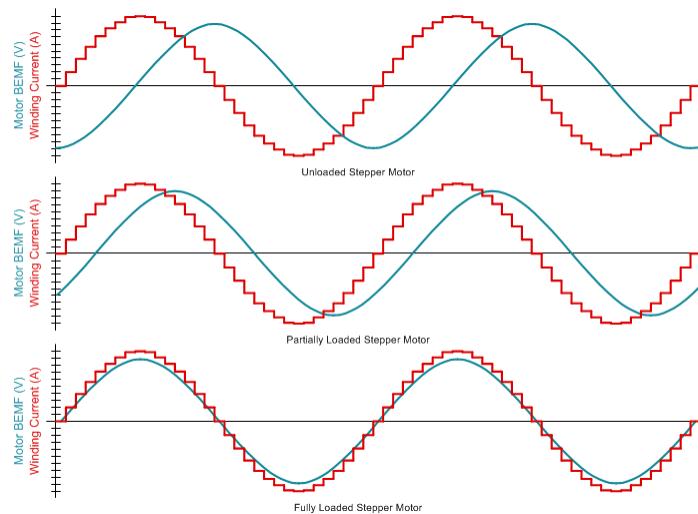

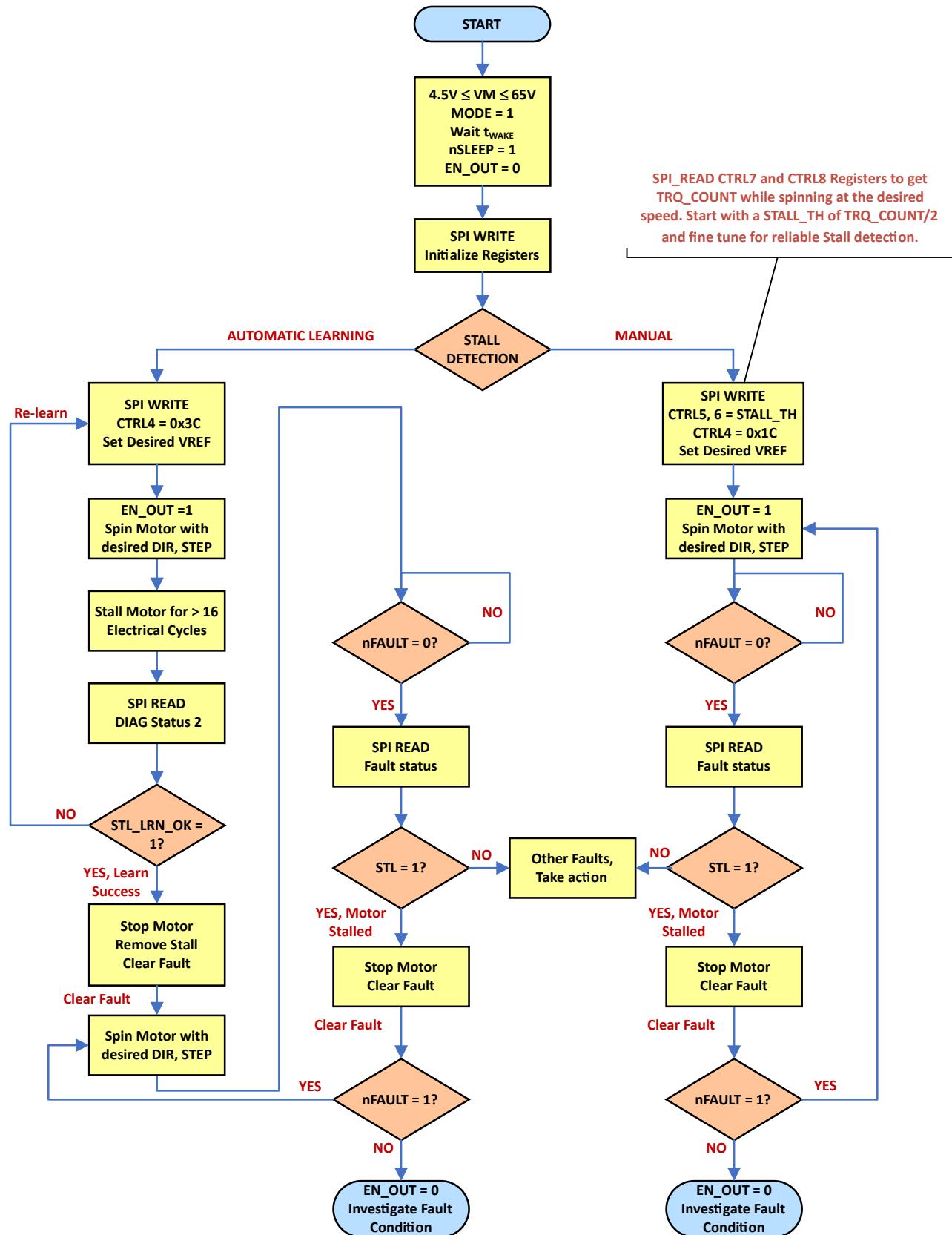

The DRV8462 integrates the auto-torque feature to reduce power loss and improve system efficiency by adjusting output current according to the load torque. The SPI interface provides various options to optimize the performance of the auto-torque algorithm for specific motor and system use case. The stall detection feature detects and reports a motor stall condition to the system controller when the motor is obstructed or has reached an end-of-travel stop. Additionally, the standstill power saving mode reduces power loss when the motor is at holding position.

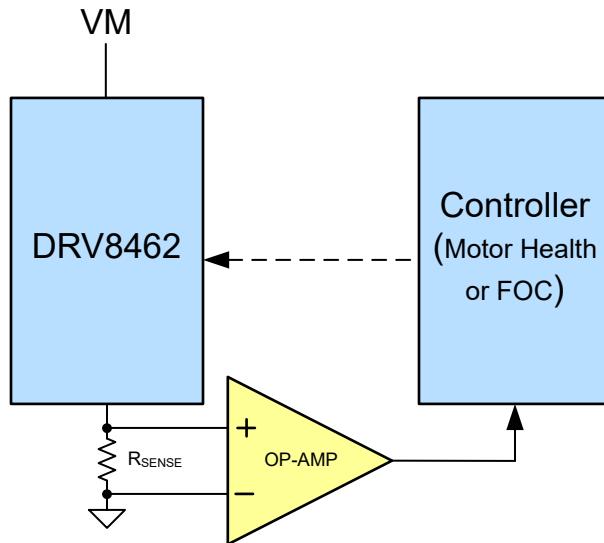

The DRV8462 uses an integrated current-sense architecture which eliminates the need for two external power sense resistors, hence saving significant board space, BOM cost, design efforts and reduces significant power consumption. This architecture eliminates the power dissipated in the sense resistors by using a current mirror approach and using the internal power MOSFETs for current sensing. Optional external power sense resistors can also be connected between the PGND pins and board ground to monitor motor health and for implementing closed-loop algorithms such as Field Oriented Control. The current regulation set point is adjusted by the voltage at the VREF pin. For the SPI interface, an 8-bit register allows the controller to scale the output current without needing to scale the VREF voltage reference; and another 8-bit register allows configuration of the holding current level for the purpose of reducing power loss at motor standstill.

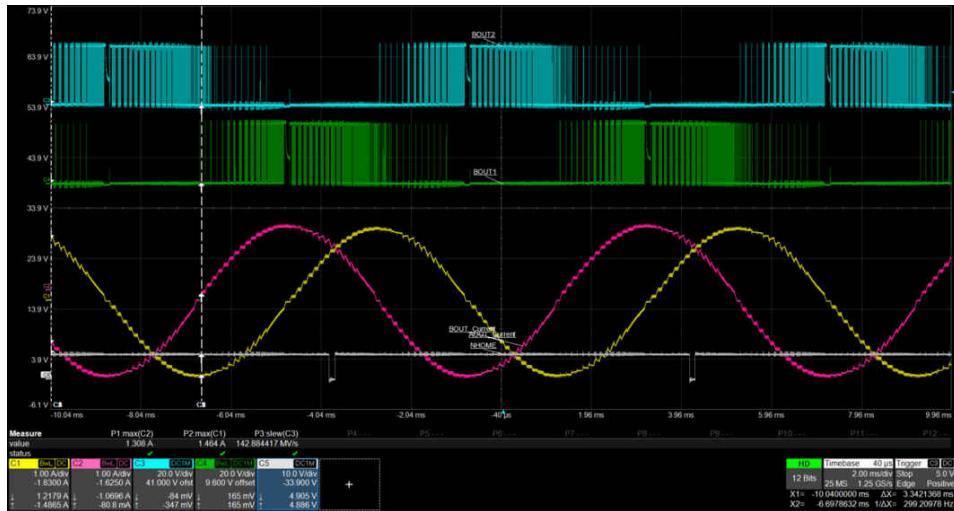

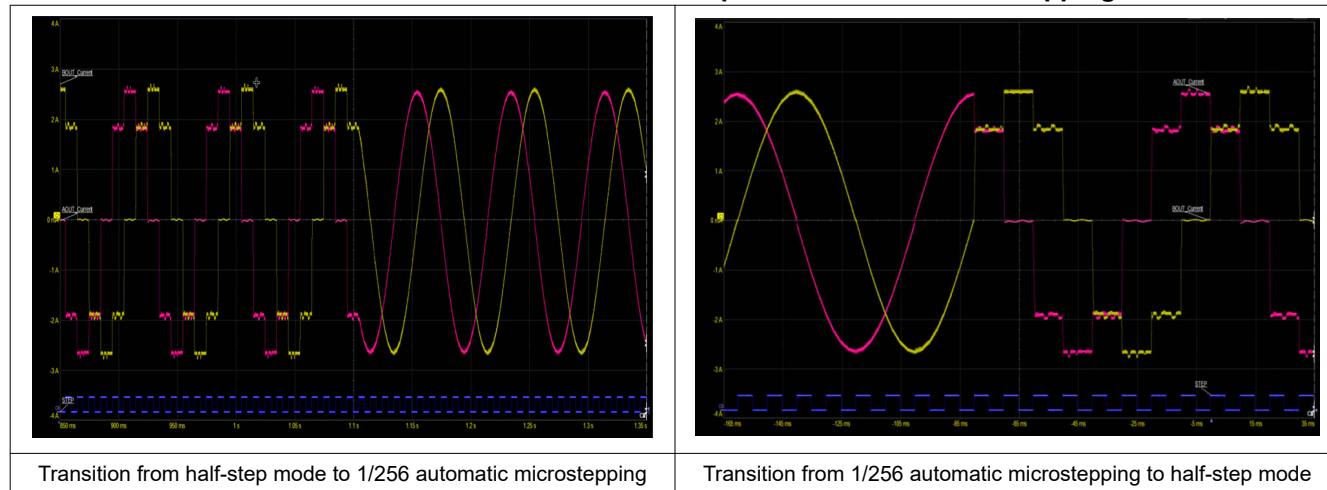

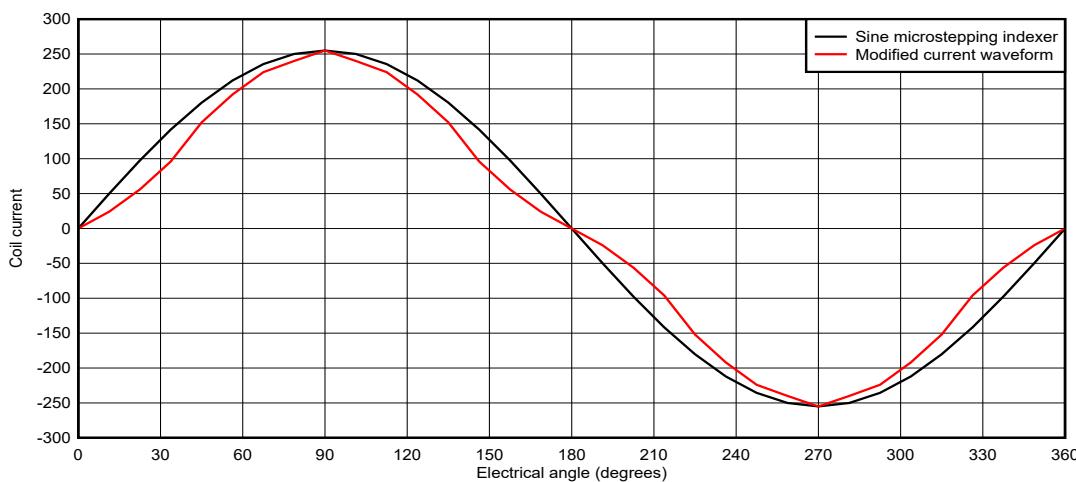

A STEP/DIR pin interface allows an external controller to manage the direction and step rate of the stepper motor. The internal microstepping indexer can execute high-accuracy micro-stepping without requiring the external controller to manage the winding current level. The indexer is capable of full step, half step, and 1/4, 1/8, 1/16, 1/32, 1/64, 1/128, and 1/256 microstepping. High microstepping contributes to significant audible noise reduction and smooth motion. The automatic microstepping mode interpolates the input step frequency to high resolution, thereby improving current regulation and reducing audible noise while running with a low frequency step input from the controller. The custom microstepping table allows adjusting the current waveform to the needs of a particular motor.

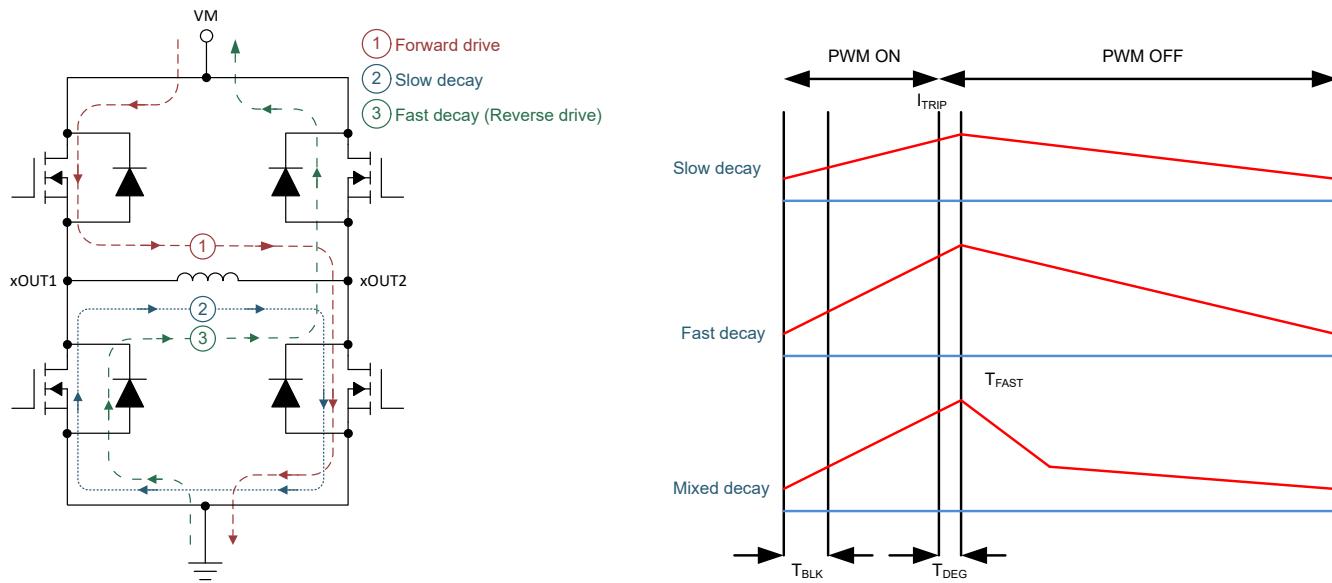

Stepper motor drivers need to re-circulate the winding current by implementing several types of decay modes, such as slow decay, mixed decay and fast decay. The DRV8462 supports smart tune decay modes. The smart tune is an innovative decay mechanism that automatically adjusts for optimal current regulation performance agnostic of supply voltage and motor speed variations and aging effects. Smart tune Ripple Control uses a variable off-time ripple current control scheme to minimize distortion of the motor winding current. Smart tune Dynamic Decay uses a fixed off-time dynamic fast decay percentage scheme. Along with the smart tune decay modes, the DRV8462 also features a silent step decay mode for noiseless operation at standstill and low speeds of rotation.

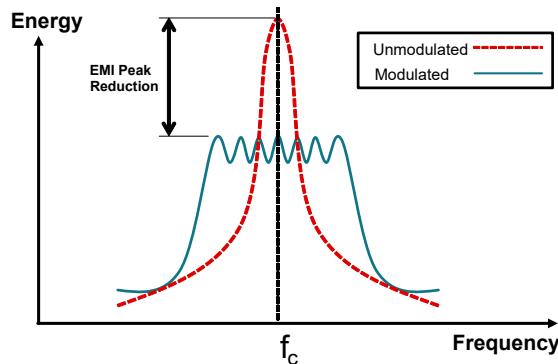

The device integrates a spread spectrum clocking feature for both the internal digital oscillator and internal charge pump. This feature minimizes the electromagnetic emissions from the device. A low-power sleep mode is included which allows the system to save power when not actively driving the motor.

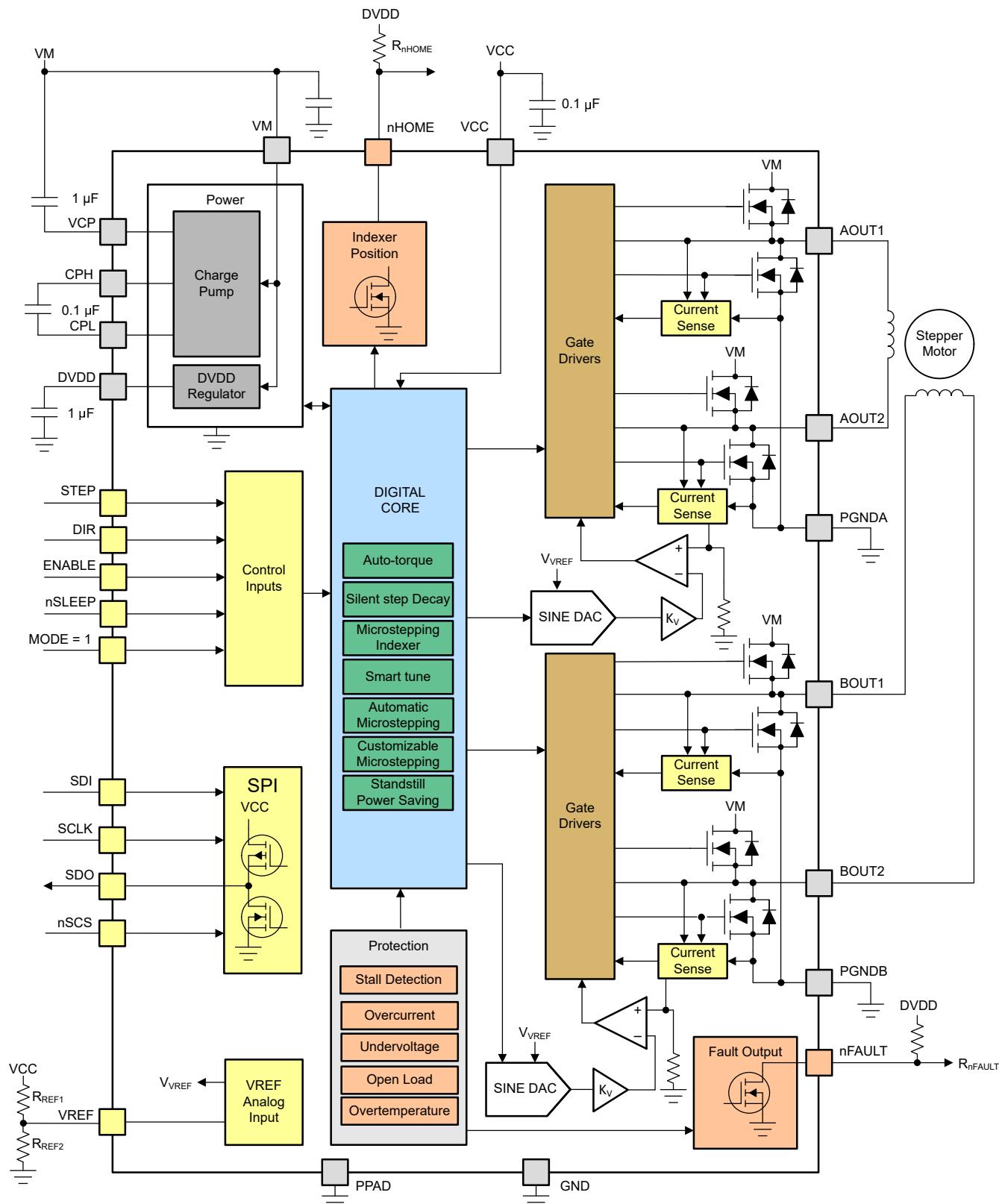

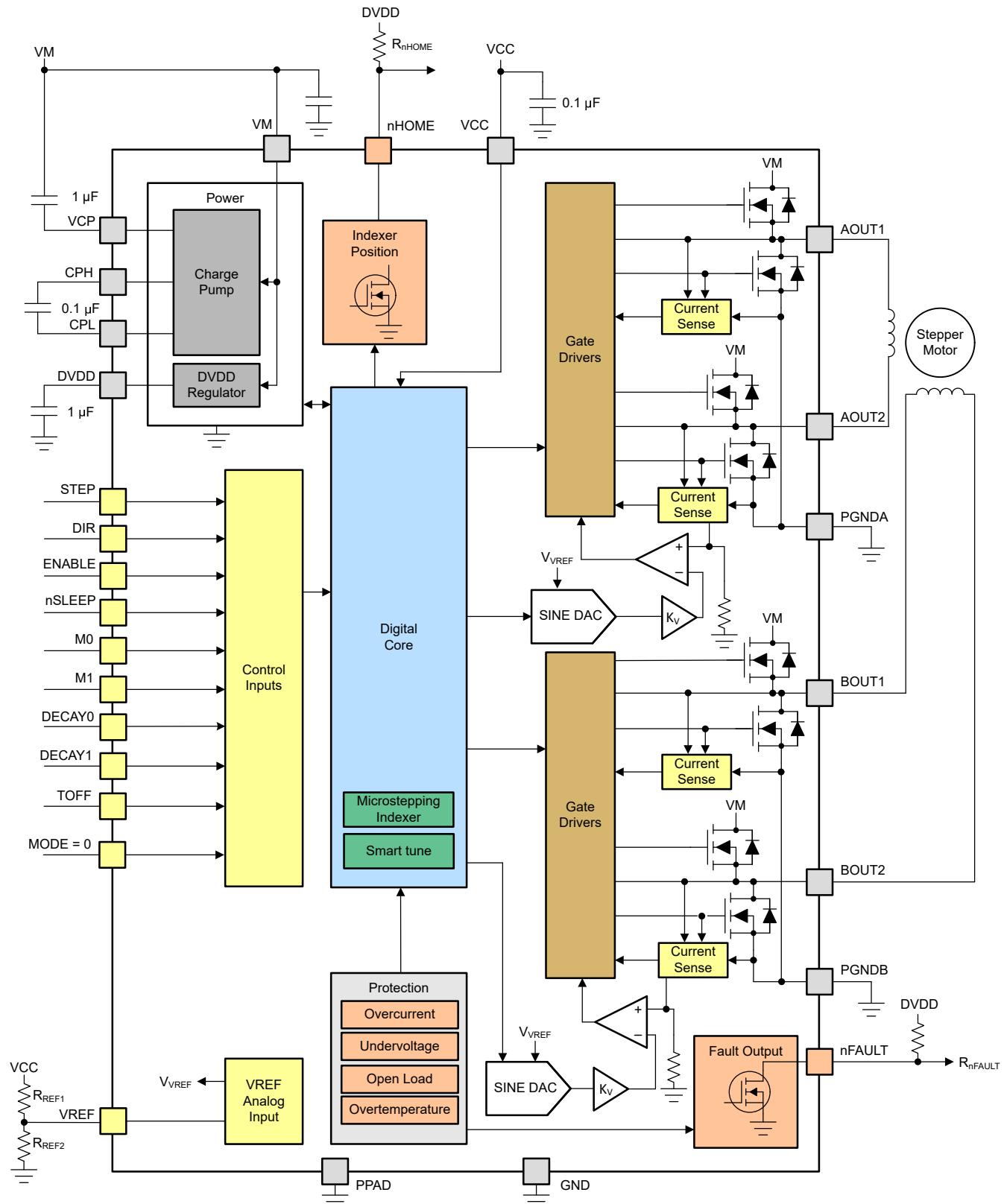

## 7.2 Functional Block Diagram

Figure 7-1. DRV8462 Block Diagram for SPI Interface

Figure 7-2. DRV8462 Block Diagram for H/W Interface

## 7.3 Feature Description

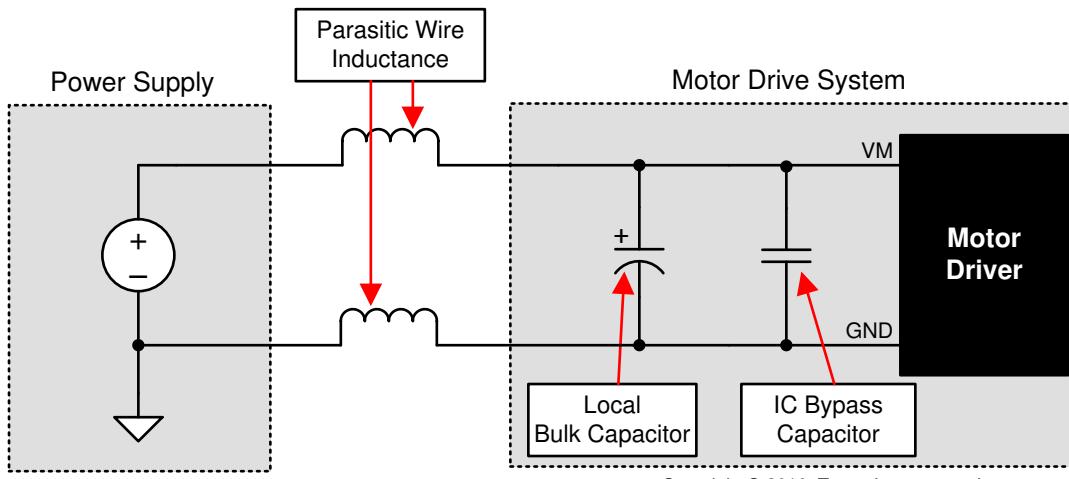

Table 7-1 lists the recommended external components for the DRV8462.

**Table 7-1. External Components**

| COMPONENT           | PIN 1       | PIN 2       | RECOMMENDED VALUE                                                   |

|---------------------|-------------|-------------|---------------------------------------------------------------------|

| C <sub>VM1</sub>    | VM          | PGNDA       | X7R, 0.01- $\mu$ F, VM-rated ceramic capacitors                     |

| C <sub>VM2</sub>    | VM          | PGNDB       | X7R, 0.01- $\mu$ F, VM-rated ceramic capacitors                     |

| C <sub>VM3</sub>    | VM          | PGNDA       | Bulk, VM-rated capacitor                                            |

| C <sub>VCP</sub>    | VCP         | VM          | X7R, 1- $\mu$ F, 16-V ceramic capacitor                             |

| C <sub>SW</sub>     | CPH         | CPL         | X7R, 0.1- $\mu$ F, VM-rated ceramic capacitor                       |

| C <sub>DVDD</sub>   | DVDD        | GND         | X7R, 1- $\mu$ F, 6.3-V ceramic capacitor                            |

| C <sub>VCC</sub>    | VCC         | GND         | X7R, 0.1- $\mu$ F, 6.3-V ceramic capacitor                          |

| R <sub>nFAULT</sub> | DVDD or VCC | nFAULT      | 10-k $\Omega$ resistor                                              |

| R <sub>nHOME</sub>  | DVDD or VCC | nHOME       | 10-k $\Omega$ resistor                                              |

| R <sub>REF1</sub>   | VREF        | DVDD or VCC | Resistor to set chopping current. Not required if VREF_INT_EN = 1b. |

| R <sub>REF2</sub>   | VREF        | GND         |                                                                     |

### 7.3.1 Interface of Operation

The DRV8462 can operate with hardware (H/W) pin interface or SPI interface. When operating with SPI interface, the device supports additional features and detailed diagnostics, as shown in Table 7-4.

The logic-level MODE pin latches the operating interface information at power up or after nSLEEP cycling -

- If the MODE pin is grounded at this time, the device operates with H/W pin interface.

- If the MODE pin is logic high at this time, the device operates with SPI interface.

---

**Note**

Do not change MODE pin logic level on the fly after power up or after nSLEEP = 1.

---

The functionality of five pins depend on the interface of operation, as shown in Table 7-2 and Table 7-3 -

**Table 7-2. Pin function, DDW package**

| Pin Number | H/W interface | SPI interface |

|------------|---------------|---------------|

| 34         | M0            | nSCS          |

| 35         | TOFF          | Reserved      |

| 36         | DECAY1        | SDO           |

| 37         | DECAY0        | SDI           |

| 38         | M1            | SCLK          |

**Table 7-3. Pin function, DDV package**

| Pin Number | H/W interface | SPI interface |

|------------|---------------|---------------|

| 29         | M1            | SCLK          |

| 30         | DECAY0        | SDI           |

| 31         | DECAY1        | SDO           |

| 32         | TOFF          | Reserved      |

| 33         | M0            | nSCS          |

Table 7-4 compares the feature set and diagnostic features for the two operating interfaces -

**Table 7-4. Feature Set for H/W and SPI interface**

| Feature                          | H/W interface | SPI interface |

|----------------------------------|---------------|---------------|

| Smart tune                       | Yes           | Yes           |

| Up to 1/256 microstepping        | Yes           | Yes           |

| VCC logic supply                 | Yes           | Yes           |

| nHOME output                     | Yes           | Yes           |

| nFAULT output                    | Yes           | Yes           |

| Automatic microstepping          | No            | Yes           |

| Customizable microstepping       | No            | Yes           |

| Indexer output                   | No            | Yes           |

| Internal 3.3 V reference voltage | No            | Yes           |

| Dual STEP active edge            | No            | Yes           |

| Silent step decay                | No            | Yes           |

| Auto-torque                      | No            | Yes           |

| Standstill power saving          | No            | Yes           |

| Spread spectrum                  | No            | Yes           |

| <b>Protection features</b>       |               |               |

| VM and VCP UVLO                  | Yes           | Yes           |

| VCC Power on Reset               | Yes           | Yes           |

| Overcurrent Protection           | Yes           | Yes           |

| Open-load detection              | Yes           | Yes           |

| Thermal shutdown                 | Yes           | Yes           |

| Stall detection                  | No            | Yes           |

| Overtemperature warning          | No            | Yes           |

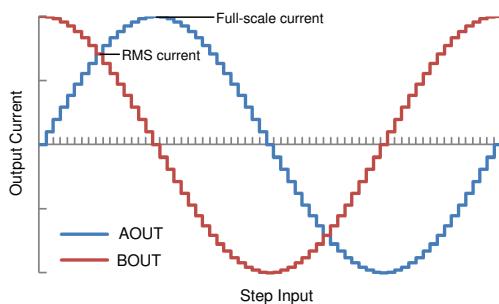

### 7.3.2 Stepper Motor Driver Current Ratings

Stepper motor drivers can be classified using three different numbers to describe the output current: peak, RMS, and full-scale.

#### 7.3.2.1 Peak Current Rating

The peak current in a stepper driver is limited by the overcurrent protection trip threshold  $I_{OCP}$ . In general the minimum value of  $I_{OCP}$  specifies the peak current rating of the stepper motor driver. For the DRV8462 in DDW package, the peak current rating is 8 A per bridge. For the DDV package, the peak current rating is 16 A per bridge.

#### 7.3.2.2 RMS Current Rating

The RMS current is determined by the thermal considerations of the IC. The RMS current is calculated based on the  $R_{DS(ON)}$ , rise and fall time, PWM frequency, device quiescent current, and package thermal performance in a typical system at 25°C. The actual operating RMS current may be higher or lower depending on heatsinking and ambient temperature. For the DRV8462 in DDW package, the RMS current rating is 3.5 A per bridge. For the DDV package, the RMS current rating is 7 A per bridge.

#### 7.3.2.3 Full-Scale Current Rating

The full-scale current describes the top of the sinusoid current waveform while microstepping. Because the sinusoid amplitude is related to the RMS current, the full-scale current is also determined by the thermal

considerations of the device. The full-scale current rating is approximately  $\sqrt{2} \times I_{RMS}$  for a sinusoidal current waveform, and  $I_{RMS}$  for a square wave current waveform (full step).

**Figure 7-3. Full-Scale and RMS Current**

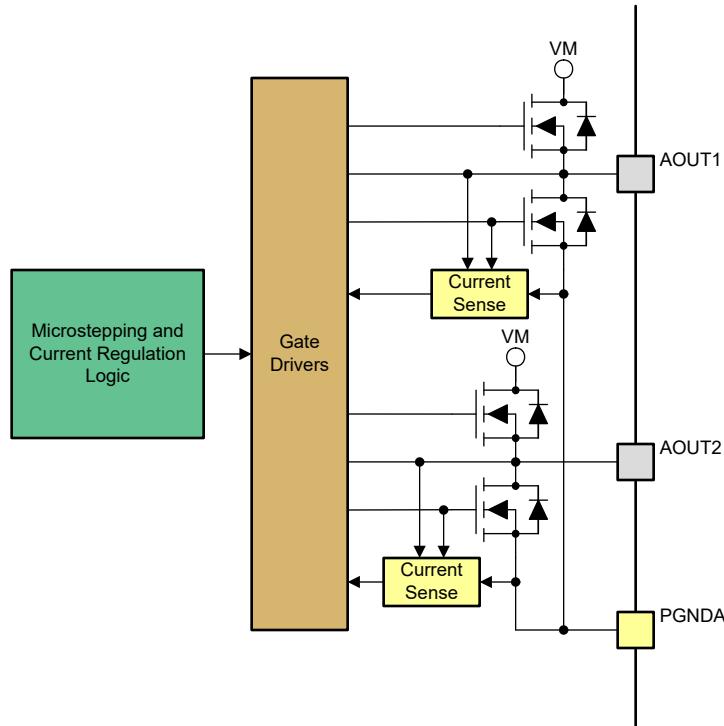

### 7.3.3 PWM Motor Drivers

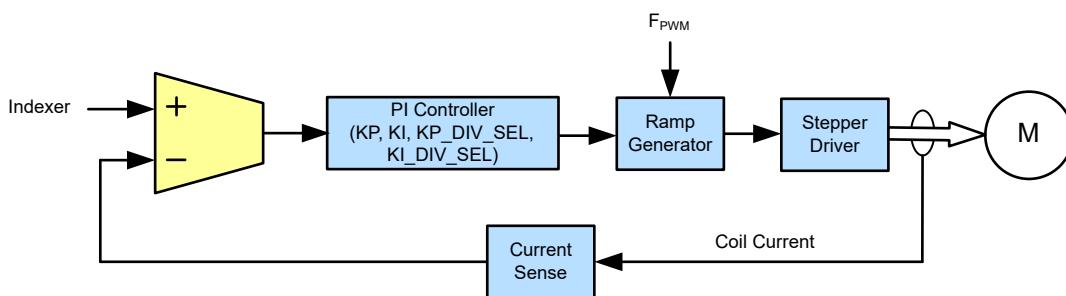

The DRV8462 has drivers for two full H-bridges to drive the two windings of a bipolar stepper motor. Figure 7-4 shows the block diagram of the circuitry.

Figure 7-4. PWM Motor Driver Block Diagram

### 7.3.4 Microstepping Indexer

Built-in indexer logic in the device allows a number of different microstep modes. The **MICROSTEP\_MODE** bits in the SPI register or the M0 and M1 pins are used to configure the step mode as shown in Table 7-5.

Table 7-5. Microstepping Indexer Settings

| MICROSTEP_MODE  | H/W Interface |               | STEP MODE                                        |

|-----------------|---------------|---------------|--------------------------------------------------|

|                 | M0            | M1            |                                                  |

| 0000b           | 0             | 0             | Full step (2-phase excitation) with 100% current |

| 0001b           | 0             | 330 kΩ to GND | Full step (2-phase excitation) with 71% current  |

| 0010b           | 1             | 0             | Non-circular 1/2 step                            |

| 0011b           | Hi-Z          | 0             | 1/2 step                                         |

| 0100b           | 0             | 1             | 1/4 step                                         |

| 0101b           | 1             | 1             | 1/8 step                                         |

| 0110b (default) | Hi-Z          | 1             | 1/16 step                                        |

| 0111b           | 0             | Hi-Z          | 1/32 step                                        |

| 1000b           | Hi-Z          | 330 kΩ to GND | 1/64 step                                        |

| 1001b           | Hi-Z          | Hi-Z          | 1/128 step                                       |

**Table 7-5. Microstepping Indexer Settings

(continued)**

| SPI Interface  | H/W Interface |      |            |

|----------------|---------------|------|------------|

| MICROSTEP_MODE | M0            | M1   | STEP MODE  |

| 1010b          | 1             | Hi-Z | 1/256 step |

When operating with SPI interface, the device allows stepping and direction change over SPI interface as well, as shown in [Table 7-6](#). Four bits are dedicated for this purpose -

**Table 7-6. STEP and DIR control over SPI**

|          |                                                  |                                                                                               |

|----------|--------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Bit      | 0b (default)                                     | 1b                                                                                            |

| SPI_DIR  | Driver changes direction based on DIR pin inputs | Direction changes depend on the DIR bit                                                       |

| SPI_STEP | Stepping depends on the STEP pin inputs          | Step changes depend on the STEP bit                                                           |

| DIR      | Motor moves in the reverse direction             | Motor moves in the forward direction                                                          |

| STEP     | X                                                | Indexer advances by one step. STEP bit is self-clearing, becomes '0' after writing '1' to it. |

[Table 7-7](#) shows the relative current and step directions for full-step (71% current), 1/2 step, 1/4 step and 1/8 step operations for the case when DIR pin is logic high or DIR bit is '1'. Higher microstepping resolutions follow the same pattern. The AOUT current is the sine of the electrical angle and the BOUT current is the cosine of the electrical angle. Positive current is defined as current flowing from the xOUT1 pin to the xOUT2 pin while driving.

**Table 7-7. Relative Current and Step Directions**

| 1/8 STEP | 1/4 STEP | 1/2 STEP | FULL STEP 71% | AOUT CURRENT (% FULL-SCALE) | BOUT CURRENT (% FULL-SCALE) | ELECTRICAL ANGLE (DEGREES) |

|----------|----------|----------|---------------|-----------------------------|-----------------------------|----------------------------|

| 1        | 1        | 1        |               | 0%                          | 100%                        | 0.00                       |

| 2        |          |          |               | 20%                         | 98%                         | 11.25                      |

| 3        | 2        |          |               | 38%                         | 92%                         | 22.50                      |

| 4        |          |          |               | 56%                         | 83%                         | 33.75                      |

| 5        | 3        | 2        | 1             | 71%                         | 71%                         | 45.00                      |

| 6        |          |          |               | 83%                         | 56%                         | 56.25                      |

| 7        | 4        |          |               | 92%                         | 38%                         | 67.50                      |

| 8        |          |          |               | 98%                         | 20%                         | 78.75                      |

| 9        | 5        | 3        |               | 100%                        | 0%                          | 90.00                      |

| 10       |          |          |               | 98%                         | -20%                        | 101.25                     |

| 11       | 6        |          |               | 92%                         | -38%                        | 112.50                     |

| 12       |          |          |               | 83%                         | -56%                        | 123.75                     |

| 13       | 7        | 4        | 2             | 71%                         | -71%                        | 135.00                     |

| 14       |          |          |               | 56%                         | -83%                        | 146.25                     |

| 15       | 8        |          |               | 38%                         | -92%                        | 157.50                     |

| 16       |          |          |               | 20%                         | -98%                        | 168.75                     |

| 17       | 9        | 5        |               | 0%                          | -100%                       | 180.00                     |

| 18       |          |          |               | -20%                        | -98%                        | 191.25                     |

| 19       | 10       |          |               | -38%                        | -92%                        | 202.50                     |

| 20       |          |          |               | -56%                        | -83%                        | 213.75                     |

| 21       | 11       | 6        | 3             | -71%                        | -71%                        | 225.00                     |

| 22       |          |          |               | -83%                        | -56%                        | 236.25                     |

| 23       | 12       |          |               | -92%                        | -38%                        | 247.50                     |

**Table 7-7. Relative Current and Step Directions (continued)**

| 1/8 STEP | 1/4 STEP | 1/2 STEP | FULL STEP 71% | AOUT CURRENT (% FULL-SCALE) | BOUT CURRENT (% FULL-SCALE) | ELECTRICAL ANGLE (DEGREES) |

|----------|----------|----------|---------------|-----------------------------|-----------------------------|----------------------------|

| 24       |          |          |               | -98%                        | -20%                        | 258.75                     |

| 25       | 13       | 7        |               | -100%                       | 0%                          | 270.00                     |

| 26       |          |          |               | -98%                        | 20%                         | 281.25                     |

| 27       | 14       |          |               | -92%                        | 38%                         | 292.50                     |

| 28       |          |          |               | -83%                        | 56%                         | 303.75                     |

| 29       | 15       | 8        | 4             | -71%                        | 71%                         | 315.00                     |

| 30       |          |          |               | -56%                        | 83%                         | 326.25                     |

| 31       | 16       |          |               | -38%                        | 92%                         | 337.50                     |

| 32       |          |          |               | -20%                        | 98%                         | 348.75                     |

**Table 7-8** shows the full step operation with 100% full-scale current for the DIR = 1 case. This stepping mode consumes more power than full-step mode with 71% current, but provides a higher torque at high motor RPM.

**Table 7-8. Full Step with 100% Current**

| FULL STEP 100% | AOUT CURRENT (% FULL-SCALE) | BOUT CURRENT (% FULL-SCALE) | ELECTRICAL ANGLE (DEGREES) |

|----------------|-----------------------------|-----------------------------|----------------------------|

| 1              | 100                         | 100                         | 45                         |

| 2              | 100                         | -100                        | 135                        |

| 3              | -100                        | -100                        | 225                        |

| 4              | -100                        | 100                         | 315                        |

**Table 7-9** shows the noncircular 1/2-step operation for the DIR = 1 case. This stepping mode consumes more power than circular 1/2-step operation, but provides a higher torque at high motor RPM.

**Table 7-9. Non-Circular 1/2-Stepping Current**

| NON-CIRCULAR 1/2-STEP | AOUT CURRENT (% FULL-SCALE) | BOUT CURRENT (% FULL-SCALE) | ELECTRICAL ANGLE (DEGREES) |

|-----------------------|-----------------------------|-----------------------------|----------------------------|

| 1                     | 0                           | 100                         | 0                          |

| 2                     | 100                         | 100                         | 45                         |

| 3                     | 100                         | 0                           | 90                         |

| 4                     | 100                         | -100                        | 135                        |

| 5                     | 0                           | -100                        | 180                        |

| 6                     | -100                        | -100                        | 225                        |

| 7                     | -100                        | 0                           | 270                        |

| 8                     | -100                        | 100                         | 315                        |

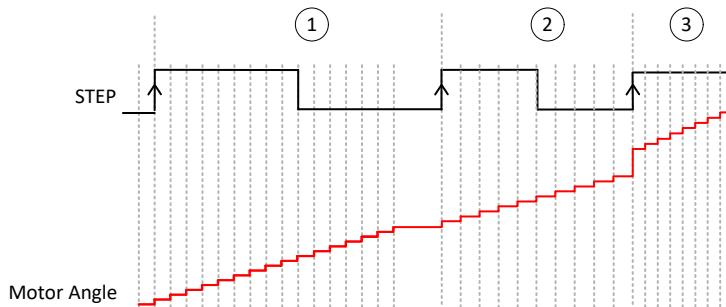

When operating with the SPI interface, depending on the STEP\_EDGE bit, STEP active edge can be either rising edge or both rising and falling edge, as shown in **Table 7-10**. When configured with H/W interface, the STEP active edge is only the rising edge. For applications that need to run at high input STEP rate, configuring both edges as active edge reduces controller overhead by half, because the input STEP rate is effectively doubled.

**Table 7-10. STEP Active Edge**

| Interface | STEP_EDGE    | STEP Active Edge             |

|-----------|--------------|------------------------------|

| SPI       | 0b (default) | Rising edge                  |

|           | 1b           | Rising edge and falling edge |

| H/W       | X            | Rising edge                  |

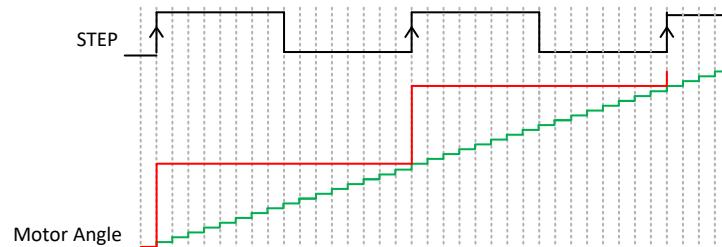

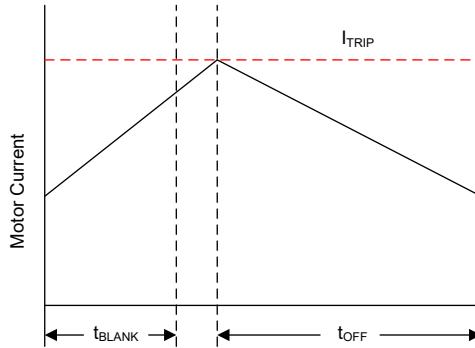

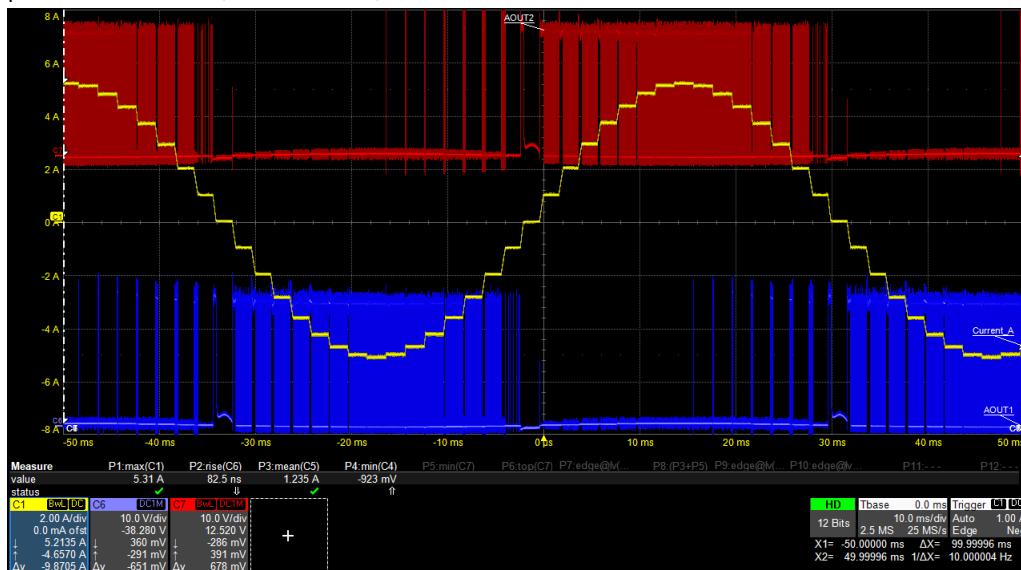

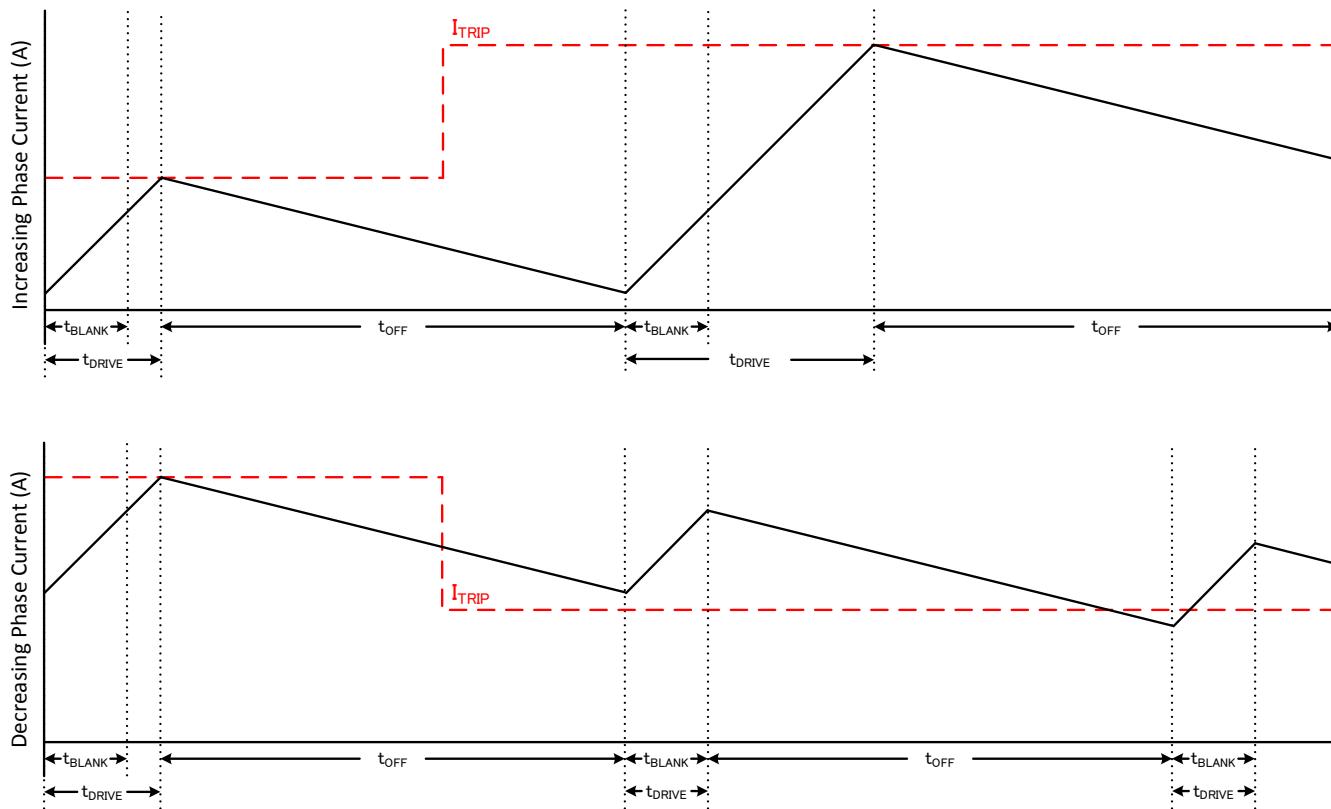

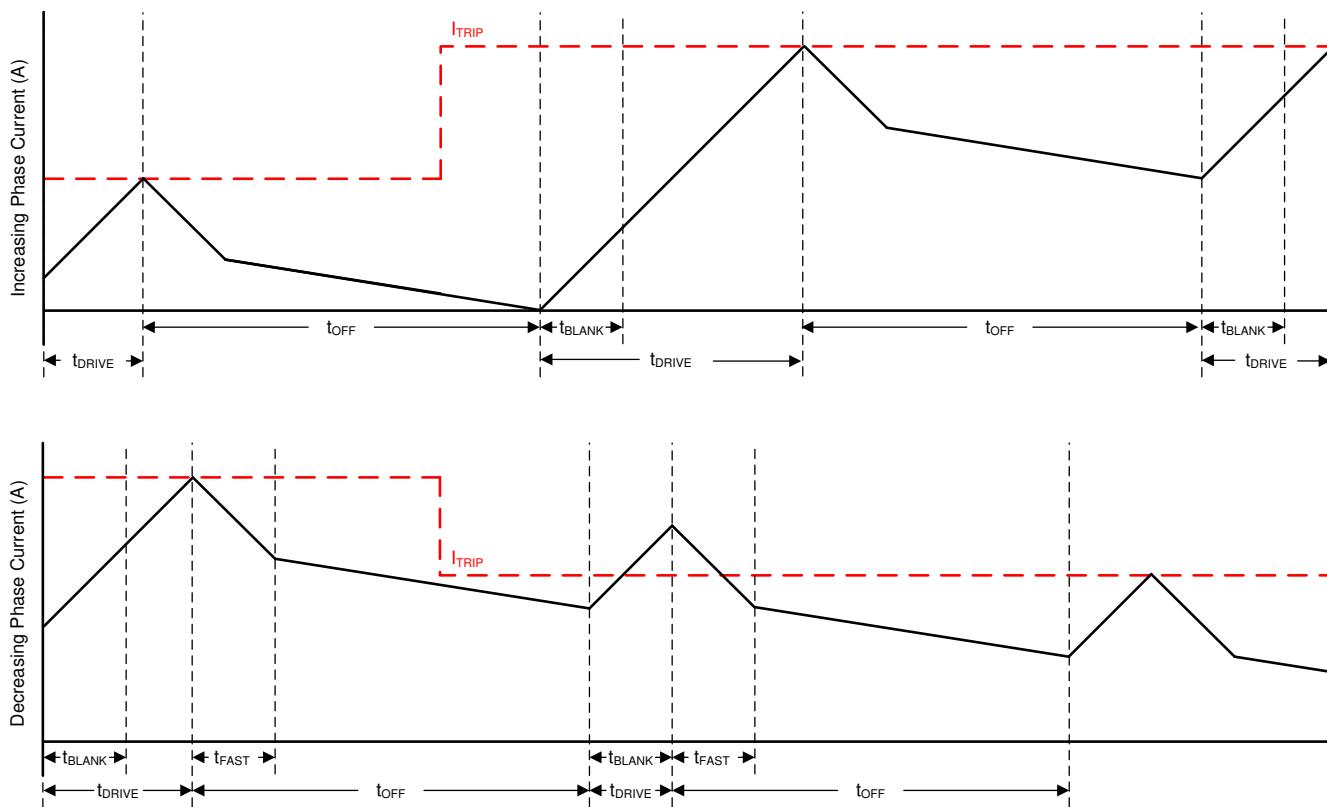

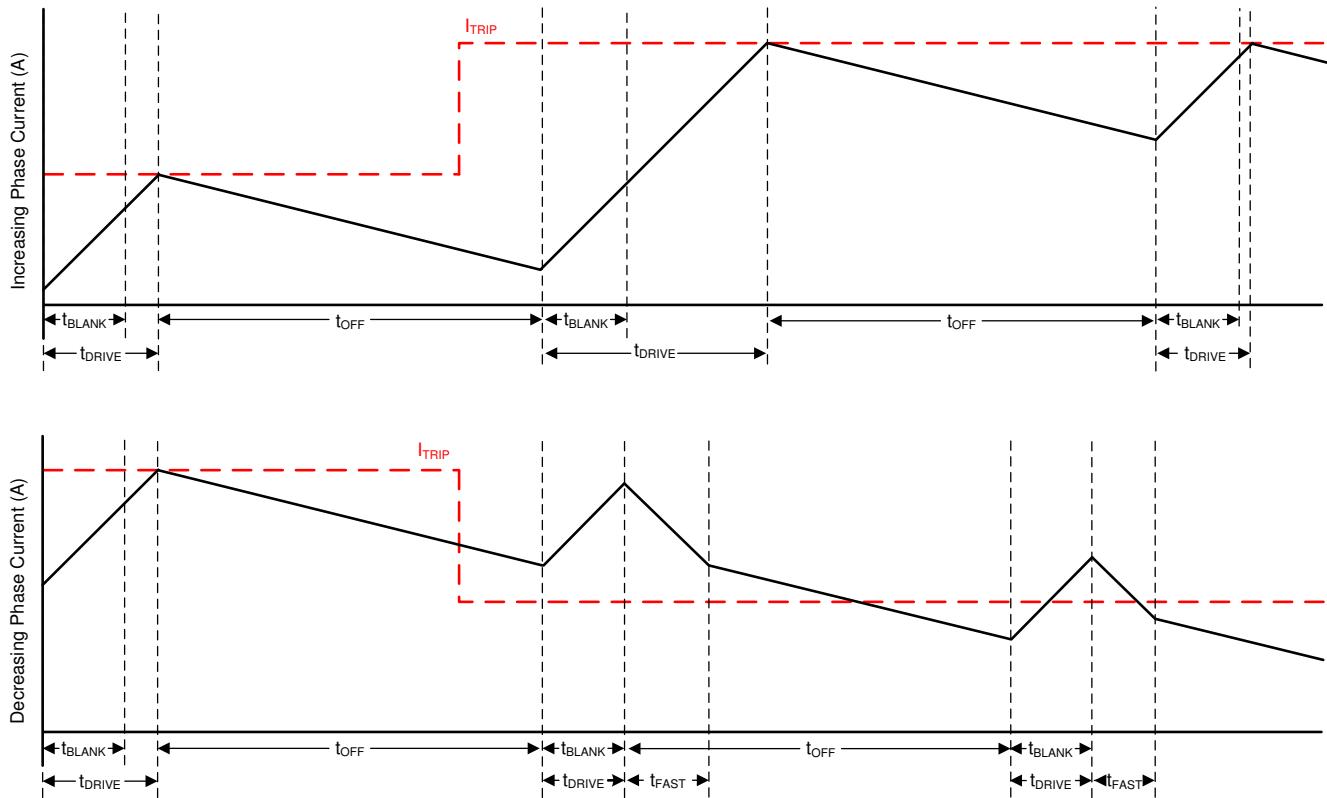

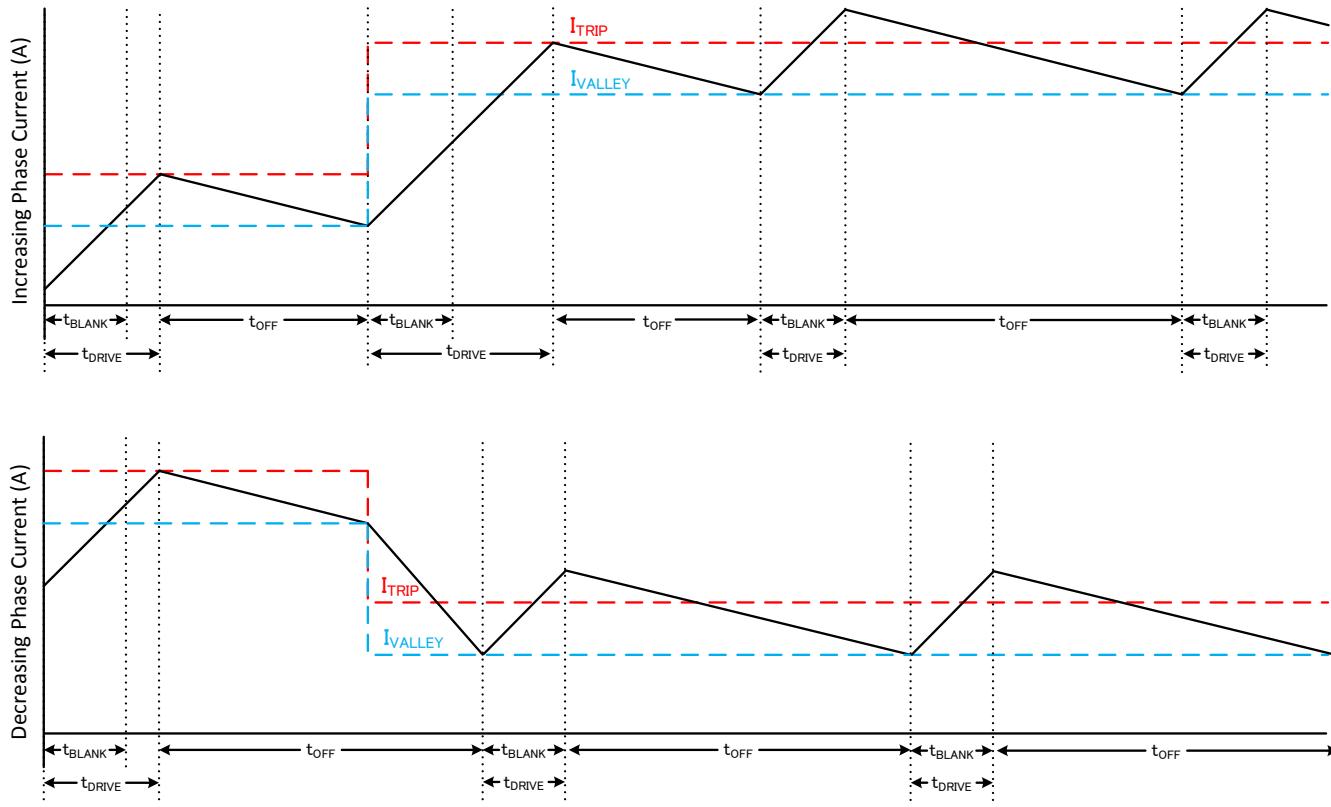

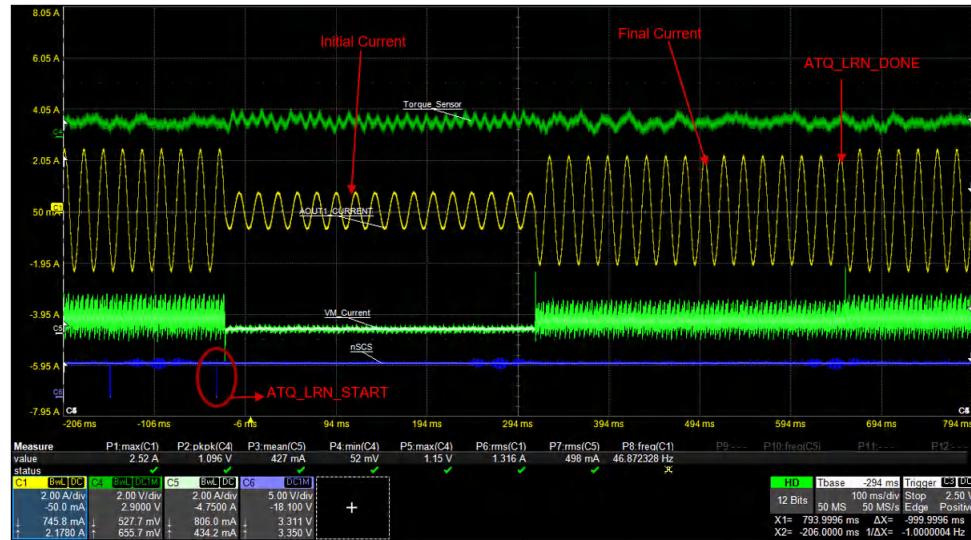

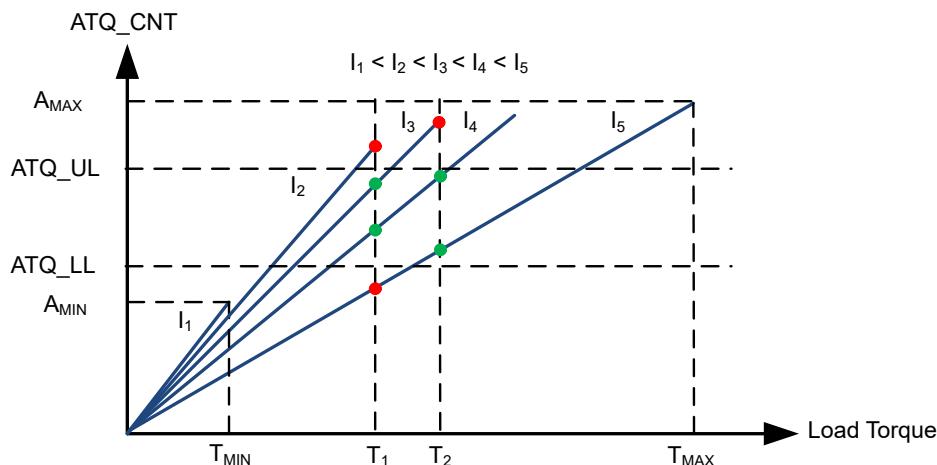

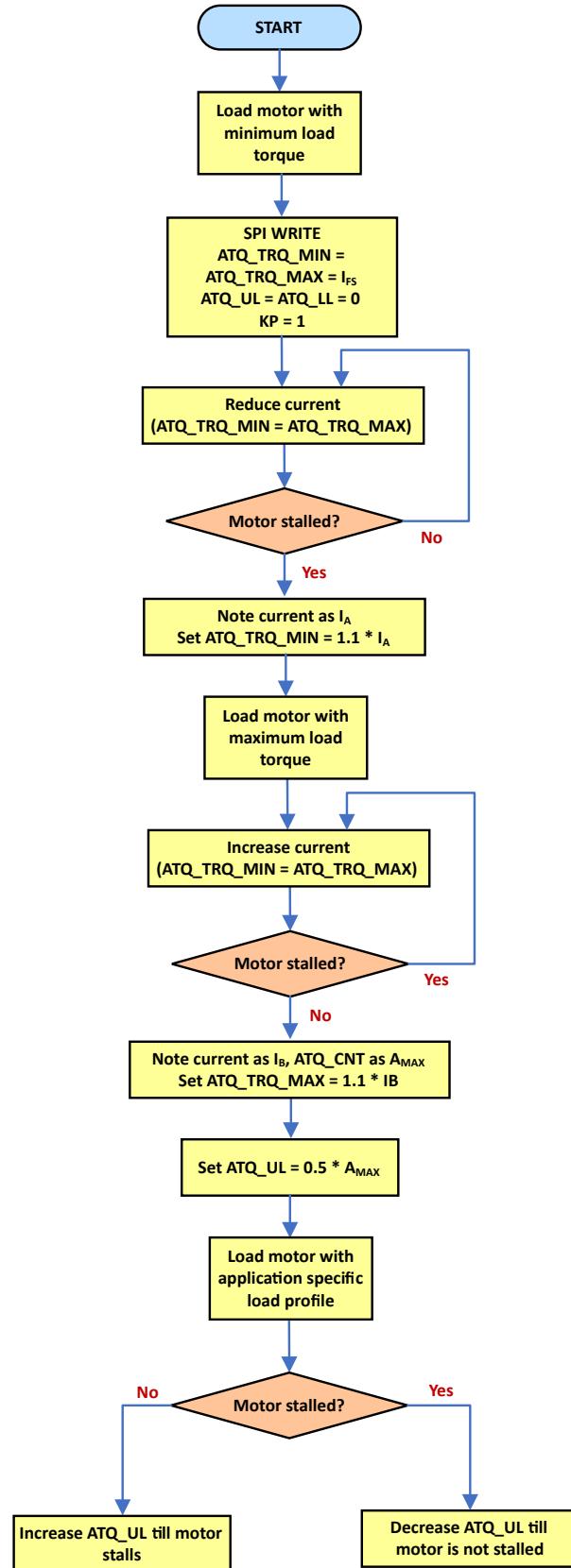

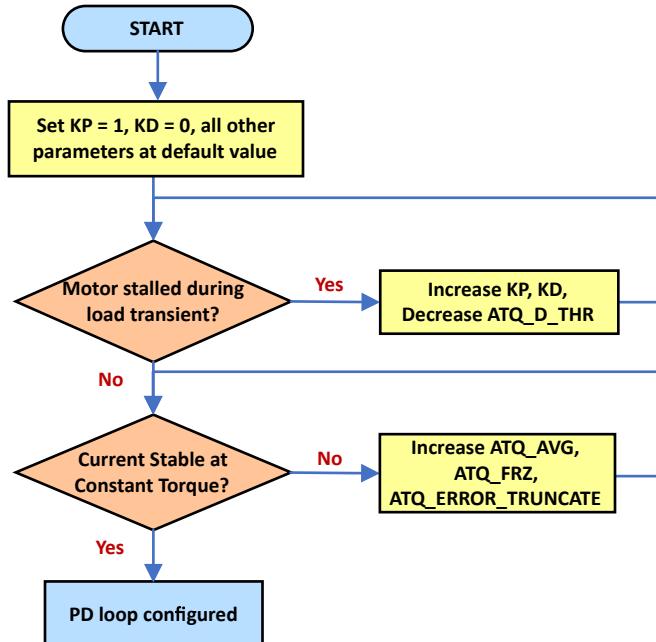

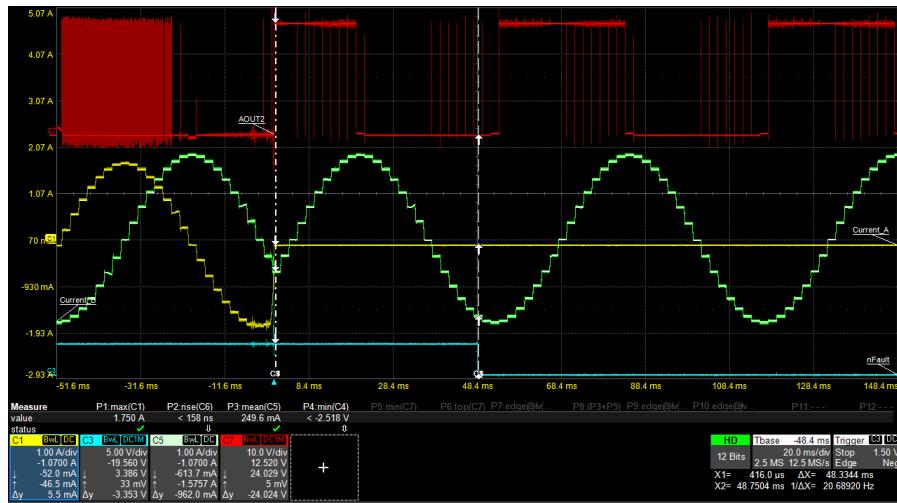

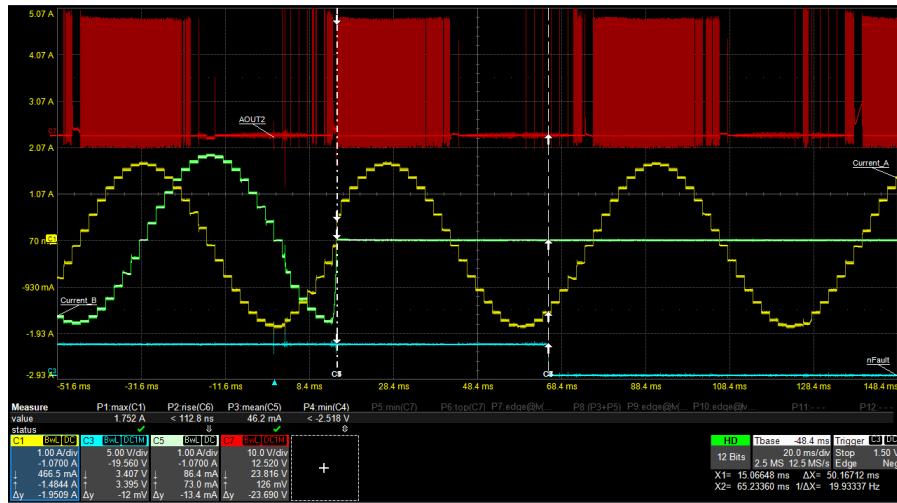

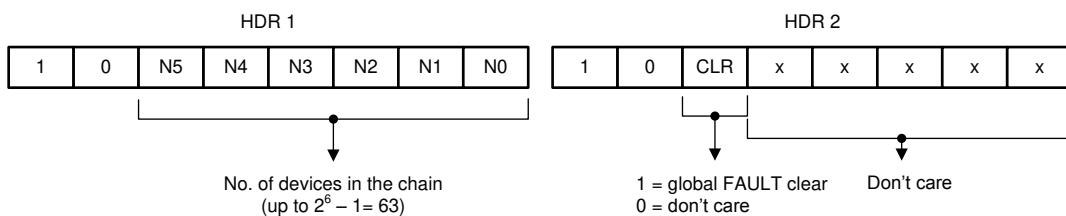

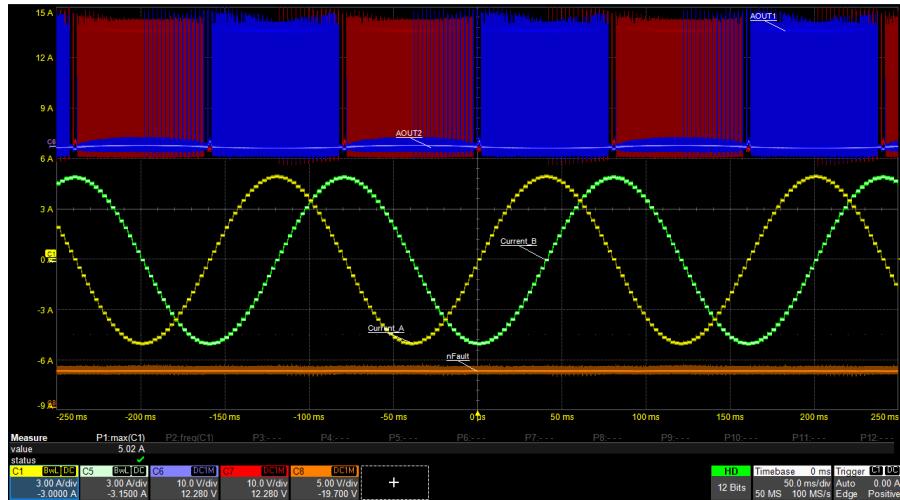

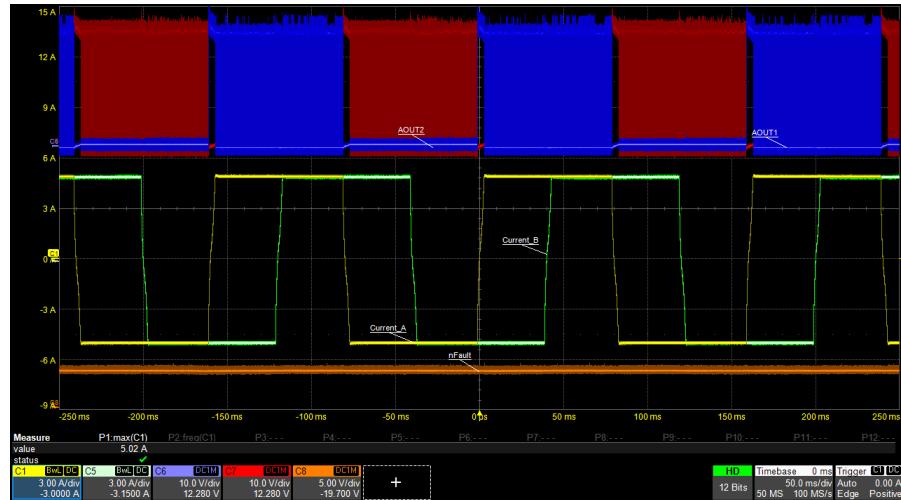

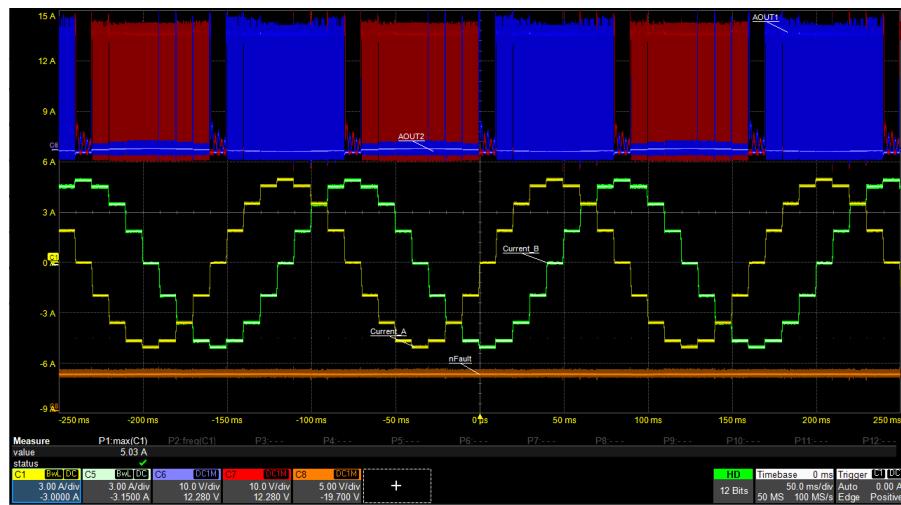

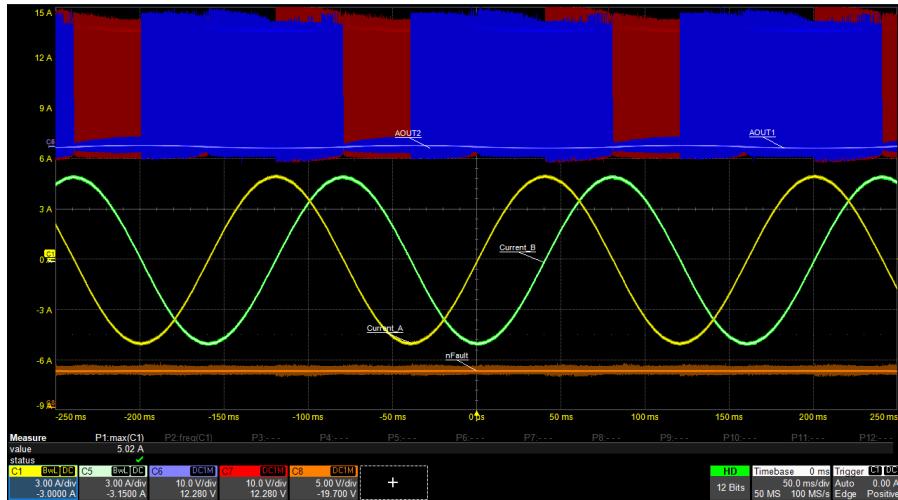

At each active edge of the STEP input the indexer advances to the next state in the table. The direction shown is with the DIR pin logic high. If the DIR pin is logic low, the sequence table is reversed. If the step mode is changed dynamically while stepping, the indexer advances to the next valid state for the new step mode setting at the active edge of STEP.